## EPIC Final Report

| Program        | Electric Program Investment Charge (EPIC)                            |

|----------------|----------------------------------------------------------------------|

| Administrator  | San Diego Gas & Electric Company                                     |

| Project Number | EPIC-1, Project 5                                                    |

| Project Name   | Smart Distribution Circuit Demonstrations                            |

| Module Name    | Module 1, Demonstrations of Advanced Circuit<br>Concepts and Devices |

| Date           | December 31, 2017                                                    |

## Attribution

This comprehensive final report documents the work done in this EPIC project. The project team for this work included the following individuals, listed alphabetically by last name.

## Internal SDG&E Project Technical Team

Aksel Encinas Frank Goodman Molham Kayali Amin Salmani Aung Thant

### Internal SDG&E Stakeholder Review Panel

Laurence Abcede Kahveh Atef

Michael Colburn

Jamie Exon

Christian Henderson

Karl Iliev

Greg Smith

Jade Thiemsuwan

Stacy Williams

### Schweitzer Engineering Laboratories, Inc.

Alaap Anujan

Arvind Ayilliath

Tanushri Doshi

Kamal Garg

Jenny Hitch

Cassie Reimer

## **EXECUTIVE SUMMARY**

**Program Objective:** The objective of SDG&E's EPIC-1, Project 5, on Smart Distribution Circuit Demonstrations, was to perform pilot demonstrations of smart distribution circuit features and associated simulation work to identify best practices for integrating new and existing distribution equipment in these circuits. The project was broken into two modules:

- Demonstration of Advanced Circuit Concepts

- Demonstration of Methodologies and Tools for Energy Storage System Assessment

This executive summary describes the work and results for the first module. The work on pre-commercial demonstration of advanced circuit concepts was broadly divided into three phases:

**Phase 1** included evaluation of products and technologies currently available for improved distribution circuit design, system operation, and protection. It also assessed emerging distribution circuit solutions for maintaining reliable and uninterrupted energy delivery. Hardware evaluation covered topics such as time synchronization, protection and automation control, communication, and renewables and energy storage. Some of the distribution solutions investigated include advanced distribution automation control, dynamic feeder optimization, synchrophasor-based solutions, and fault location.

**Phase 2** included the selection and modeling of three distribution circuits: coastal-residential, desert-rural, and urban. The circuit parameters provided by SDG&E in Synergi Electric format were converted to RTDS Power Simulation Software (RSCAD) and validated for accuracy. A pre-commercial demonstration plan was developed to validate the distribution circuit operation and equipment performance. A hardware setup was assembled for pre-commercial demonstration of the performance of individual smart devices in a laboratory. Algorithms were developed to study system voltage coordination on distribution circuits between distributed energy resource (DER) and voltage regulators (VR). The interaction between the two device types was made possible with a controller at a central level. Circuit performance was studied during load switching via simulations. The test observations and circuit performance were captured for further analysis.

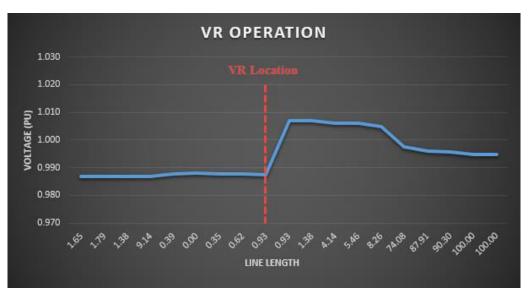

**Phase 3** included the analysis of the demonstration results carried out in Phase 2 and provided recommendations on the integration and coordination of multiple voltage correction devices on a larger system, controlled by a central master controller. It is demonstrated via simulations that the DER and VR can be controlled interactively to provide voltage support on distribution circuits. Practical implementation and expansion to include other voltage correction devices are discussed. Certain modern solutions including detection of downed conductors and power quality monitoring are discussed, offering insights on how to improve the existing distribution system.

The demonstration laid groundwork for commercial adoption of the demonstrated concepts. It is recommended that SDG&E pursue commercial adoption of some of the key concepts that were demonstrated. On larger distribution circuits with multiple voltage regulation devices, system-wide voltage coordination would be required for efficient and reliable service to the customers. This implementation would also aid in improving the lifespan of various distribution equipment, as well as lowering the associated maintenance costs. Some of the challenges associated with implementing this concept in larger circuits include bringing together devices from multiple vendors on one platform and the communication protocols supported by them. Adoption of a standardized communication architecture is recommended for this purpose. It is recommended that selected devices and communications protocols be carefully evaluated before commercial adoption. A technology transfer plan was created to include the recommended steps to bridge the gap between laboratory demonstration of improved distribution practices and its successful commercial and practical implementation in the field on larger distribution circuits.

## **Table of Contents**

| E | xecutive S | Summaryiii                                           |

|---|------------|------------------------------------------------------|

| A | bbreviatio | ons and Acronymsxviii                                |

| 1 | Introdu    | ıction1                                              |

| 2 | Project    | Scope and Approach                                   |

|   | 2.1 Pro    | ject Initiation Meeting                              |

|   | 2.2 Pha    | ase 1 Hardware and Circuit Evaluation                |

|   | 2.3 Pha    | ase 2 Circuit Simulation and Testing Evaluation      |

|   | 2.4 Pha    | ase 3 Smart Circuit Analysis and Recommendations     |

|   | 2.5 Pro    | ject Deliverables                                    |

| 3 | Hardwa     | are and Circuit Evaluation                           |

|   | 3.1 Tin    | ne Synchronization                                   |

|   | 3.1.1      | Network Time Protocol                                |

|   | 3.1.2      | Simple Network Time Protocol                         |

|   | 3.1.3      | IRIG-B Protocol                                      |

|   | 3.1.4      | Precision Time Protocol                              |

|   | 3.1.5      | Applications7                                        |

|   | 3.2 Pro    | tection, Automation, and Control                     |

|   | 3.2.1      | Dynamic Voltage Controller7                          |

|   | 3.2.1.     | 1 Modes of Operation                                 |

|   | 3.2        | .1.1.1 Protection Mode                               |

|   | 3.2        | .1.1.2 Standby Mode                                  |

|   | 3.2        | .1.1.3 Injection/Boost Mode                          |

|   | 3.2.1.     | 2 DVR Voltage Injection Methods                      |

|   | 3.2.1.     | 3 Dynamic Volt-Ampere Reactive Compensation Solution |

|   | 3.2.1.4    | 4 D-VAR System Specifications                        |

|   | 3.2.2      | SCADA Capacitor                                      |

|   | 3.2.2.     | 1 Vendor K Automatic Capacitor Controls              |

|   | 3.2.3      | Voltage Regulator                                    |

|   | 3.2.3.     | 1 Basic Operation of a Step-Voltage Regulator        |

|   | 3.2.3.     | 2 Determining Voltage Regulator Type and Size        |

|   | 3.2.3.     | 3 Vendor D Voltage Regulator                         |

|   | 3.2.4      | Reclosers                                            |

| 3.2.4.1 Types of Reclosers                                           |  |

|----------------------------------------------------------------------|--|

| 3.2.4.1.1 Single-Phase Reclosers                                     |  |

| 3.2.4.1.2 Three-Phase Reclosers                                      |  |

| 3.2.4.1.3 Triple-Single Reclosers                                    |  |

| 3.2.4.2 Recloser Controls                                            |  |

| 3.2.4.2.1 Hydraulic Recloser Controls                                |  |

| 3.2.4.2.2 Electronic Recloser Controls                               |  |

| 3.2.4.3 Vendor G Three-Phase Reclosers                               |  |

| 3.2.4.3.1 Operating Principle                                        |  |

| 3.2.4.4 Vendor L Advanced Recloser Control                           |  |

| 3.2.5 Sectionalizers                                                 |  |

| 3.2.5.1 Selection Criteria                                           |  |

| 3.2.6 Transformer Monitoring and Control                             |  |

| 3.2.6.1 Thermal Monitoring                                           |  |

| 3.2.6.2 Dissolved Gas Analysis                                       |  |

| 3.2.6.3 Frequency Response Analysis                                  |  |

| 3.2.6.3.1 Impulse Frequency Response Analysis                        |  |

| 3.2.6.3.2 Sweep Frequency Response Analysis                          |  |

| 3.2.6.4 Partial Discharge Analysis                                   |  |

| 3.2.6.5 Microprocessor-Based Transformer Monitor                     |  |

| 3.2.7 Micro-PMU                                                      |  |

| 3.2.7.1 Components of a PMU                                          |  |

| 3.2.7.2 Need for PMUs                                                |  |

| 3.2.7.2.1 Oscillation Detection                                      |  |

| 3.2.7.2.2 Frequency Monitoring                                       |  |

| 3.2.7.2.3 Voltage Stability Monitoring                               |  |

| 3.2.7.2.4 Disturbance Detection and Alarming                         |  |

| 3.2.7.2.5 Resource Integration                                       |  |

| 3.2.7.2.6 Transmission Line Dynamic Rating and Congestion Management |  |

| 3.2.7.3 MicroPMU                                                     |  |

| 3.3 Communications                                                   |  |

| 3.3.1 Communications Protocols Used in Substations                   |  |

| 3.3.1.1 Distributed Network Protocol                                 |  |

| 3.3.1.1.1 Features of DNP3                                           |  |

| 3.3.1.2 IEC 61850 Standard                                           |  |

| 3.3.1.2.1 Features of IEC 61850                                |    |

|----------------------------------------------------------------|----|

| 3.3.1.3 GOOSE Messaging                                        |    |

| 3.3.1.4 Modbus                                                 |    |

| 3.3.2 Implementing SCADA Over Wireless Communications Networks |    |

| 3.3.2.1 Wireless Network Topologies                            |    |

| 3.3.2.2 Wireless Technologies                                  |    |

| 3.3.2.2.1 ZigBee                                               |    |

| 3.3.2.2.2 Wi-Fi                                                |    |

| 3.3.2.2.3 Worldwide Interoperability for Microwave Access      |    |

| 3.4 Renewables and Energy Storage                              |    |

| 3.4.1 Multifunction Inverters                                  |    |

| 3.4.1.1 Vendor C Solar Inverter                                |    |

| 3.4.2 Community Energy Storage (25–100 kW)                     |    |

| 3.4.2.1 Introduction                                           |    |

| 3.4.2.2 Industrial Solutions and Products                      |    |

| 3.4.2.2.1 Physical Layout                                      |    |

| 3.4.2.2.2 Operational Principle                                |    |

| 3.4.2.2.3 Device Management                                    |    |

| 3.4.2.2.4 Relevant Standards Compliance                        |    |

| 3.4.3 Commercial Electric Vehicle Supply Equipment Clusters    |    |

| 3.4.3.1 Introduction                                           |    |

| 3.4.3.2 Commercial EVSE Clusters                               |    |

| 3.4.3.3 Charging Options                                       |    |

| 3.4.3.4 Electrical Assessment of Site Prior to Installation    |    |

| 3.4.3.5 Industrial Solutions and Products                      |    |

| 3.4.3.5.1 Basic EVSE                                           |    |

| 3.4.3.5.2 Smart EVSE                                           |    |

| 3.4.3.6 Relevant Standards Compliance                          |    |

| 3.4.4 Microgrid Solutions                                      | 41 |

| 4 Solutions Evaluation                                         |    |

| 4.1 Advanced Distribution Automation Control                   |    |

| 4.1.1 Automatic Reconfiguration                                |    |

| 4.1.1.1 Feeder Event Sequence                                  |    |

| 4.1.1.2 Feeder Return-to-Normal Sequence                       |    |

| 4.1.1.3 Scheme Solution Sequence                               |    |

|   | 4.1.1.4  | Permanent Fault Condition                         | 46 |

|---|----------|---------------------------------------------------|----|

|   | 4.1.1.5  | Open-Phase Condition                              | 46 |

|   | 4.1.1.6  | Overload Condition                                | 46 |

|   | 4.1.2    | Dynamic Feeder Optimization                       | 47 |

|   | 4.1.2.1  | Distribution Unit Control                         | 47 |

|   | 4.1.2.2  | DFO Sequence of Operation                         | 48 |

|   | 4.1.2.3  | Availability of Control Actions                   | 49 |

|   | 4.1.2.4  | Regulator Response                                | 49 |

|   | 4.1.2.5  | Capacitor Response                                | 49 |

|   | 4.1.2.6  | DFO and Device Control Modes                      | 50 |

|   | 4.1.2.7  | Capacitor Calibration                             | 50 |

|   | 4.2 PM   | U-Enabled Solutions                               | 50 |

|   | 4.2.1    | Islanding Detection                               | 51 |

|   | 4.2.2    | Phase Identification                              | 51 |

|   | 4.2.3    | Load Characterization                             | 51 |

|   | 4.2.4    | System Monitoring                                 | 52 |

|   | 4.3 High | n-Impedance Fault Detection                       | 52 |

|   | 4.4 Faul | t Location                                        | 53 |

|   | 4.5 Dyn  | amic Line Rating in Distribution Circuits         | 54 |

|   | 4.6 Base | eline Data                                        | 55 |

| 5 | RTDS N   | /Iodeling                                         | 56 |

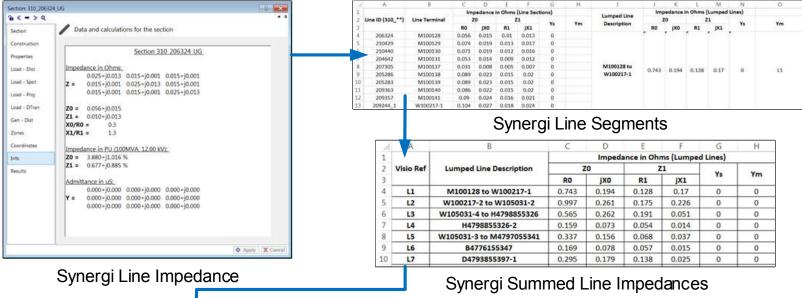

|   | 5.1 Syne | ergi to RTDS Conversion Process                   | 56 |

|   | 5.1.1    | Line Impedance Conversion – Synergi to RSCAD      | 56 |

|   | 5.1.1.1  | Line Impedance Conversion                         | 57 |

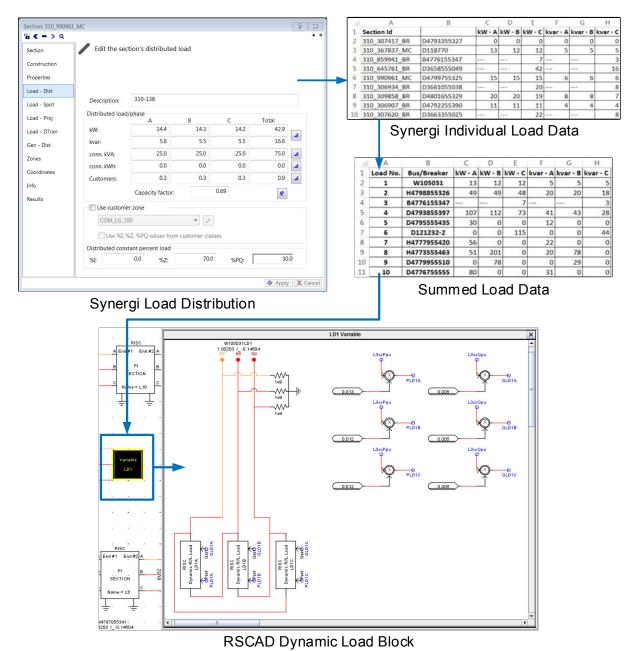

|   | 5.1.2    | Load Impedance Conversion – Synergi to RSCAD      | 58 |

|   | 5.1.2.1  | Load Impedance Conversion                         | 59 |

|   | 5.2 RTI  | DS Controller                                     | 60 |

|   | 5.2.1    | RTDS Load Impedance Controller                    | 60 |

|   | 5.2.1.1  | Load Impedance Profile and Control                | 61 |

|   | 5.3 Res  | ults Capture                                      | 64 |

| 6 | Voltage  | Regulator Control Tests                           | 65 |

|   | 6.1 Test | Setup                                             | 65 |

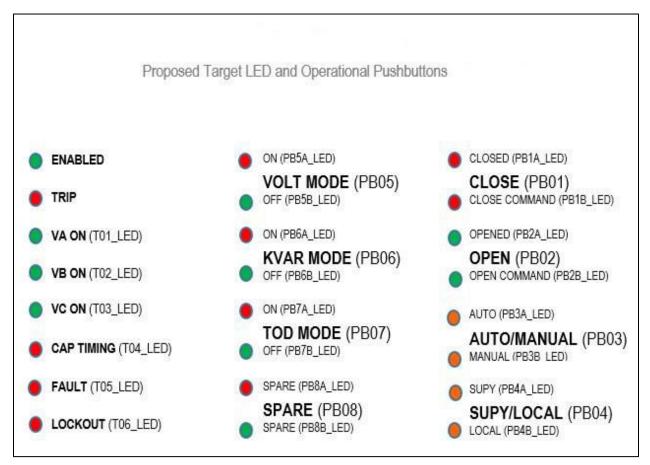

|   | 6.1.1    | Voltage Regulator Control LED Definitions         | 65 |

|   | 6.1.2    | Voltage Regulator Operator-Controlled Pushbuttons | 66 |

|   |          |                                                   |    |

| 6.1.  | 3 Voltage Regulator Control I/O List                             |  |

|-------|------------------------------------------------------------------|--|

| 6.1.  | 4 RTDS to Vendor B Amplifier Low-Level Test Interface            |  |

| 6.1.  | 5 Vendor B Amplifier to Voltage Regulator Control Test Interface |  |

| 6.2   | Operating Modes                                                  |  |

| 6.3   | Test Procedure                                                   |  |

| 6.4   | Voltage Regulator Test                                           |  |

| 6.5   | Voltage Regulator RTDS Model                                     |  |

| 6.6   | Voltage Regulator Settings                                       |  |

| 6.7   | RTDS Test Assumptions                                            |  |

| 6.8   | Test Scenarios                                                   |  |

| 6.8.  | 1 Auto and Remote Toggle – From Local Control                    |  |

| 6.8.  | 2 Automatic Voltage Regulation – Voltage Raise/Lower Operation   |  |

| 6.8.  | 3 Voltage High- and Low-Limit Scenarios – No Operation           |  |

| 6.8.  | 4 Load Profile Operation                                         |  |

| 6.9   | Recommendations                                                  |  |

| 7 Caj | pacitor Bank Controller                                          |  |

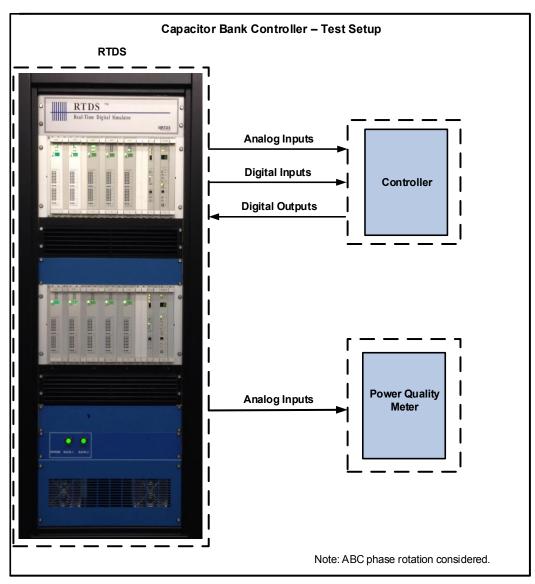

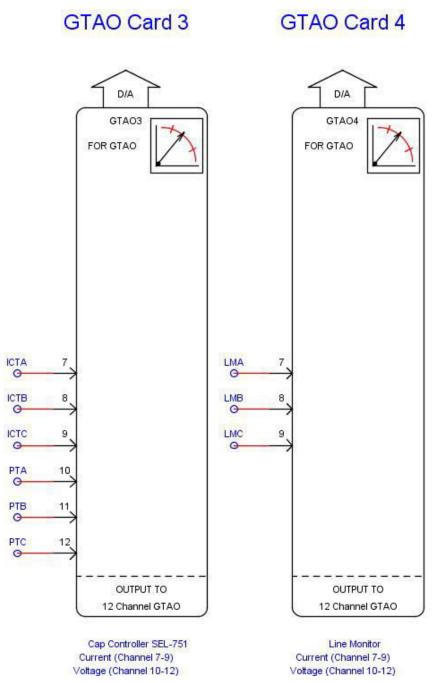

| 7.1   | Test Setup                                                       |  |

| 7.1.  | 1 I/O List                                                       |  |

| 7.1.  | 2 Front-Panel Layout                                             |  |

| 7.1.  | 3 Low-Level Test Interface                                       |  |

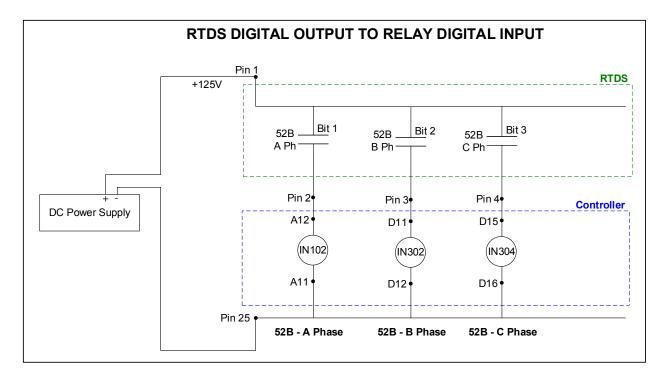

| 7.1.  | 4 RTDS and Relay Interface                                       |  |

| 7.1.  | 5 Tests Summary                                                  |  |

| 7.1.  | 6 Analog Thresholds                                              |  |

| 7.2   | Test Scenarios and Results                                       |  |

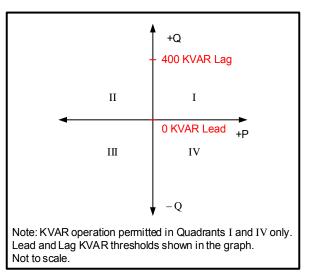

| 7.2.  | 1 SUPY and LOCAL Toggle                                          |  |

| 7.2.  | 2 AUTO and MANUAL Toggle – From LOCAL Control                    |  |

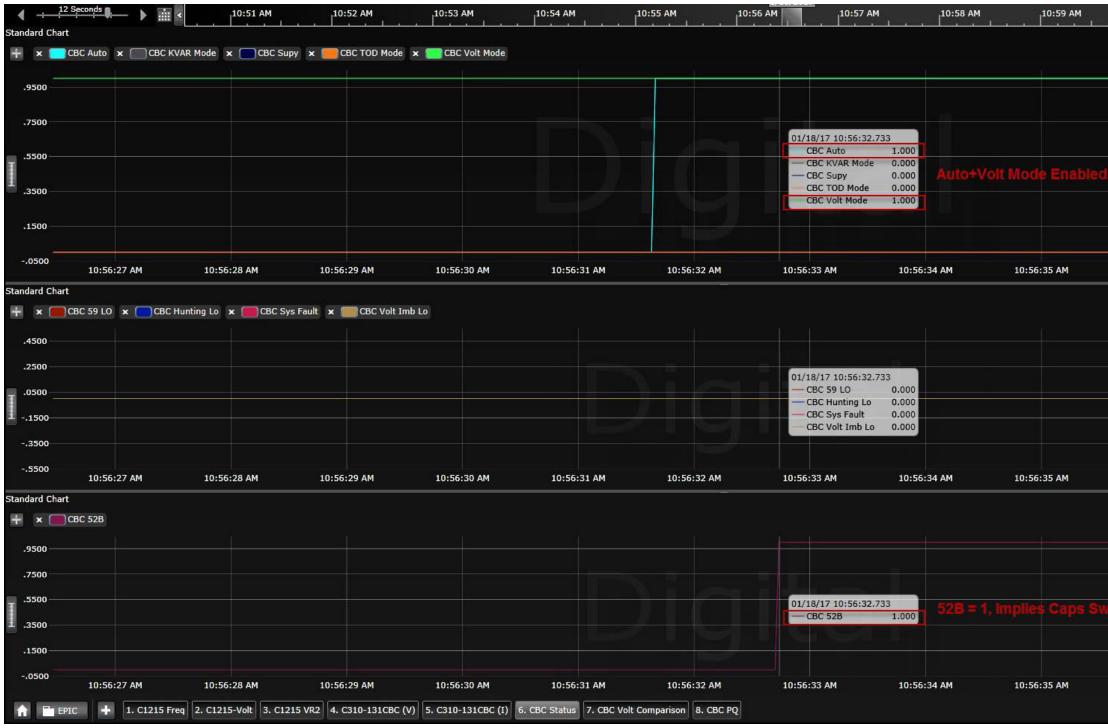

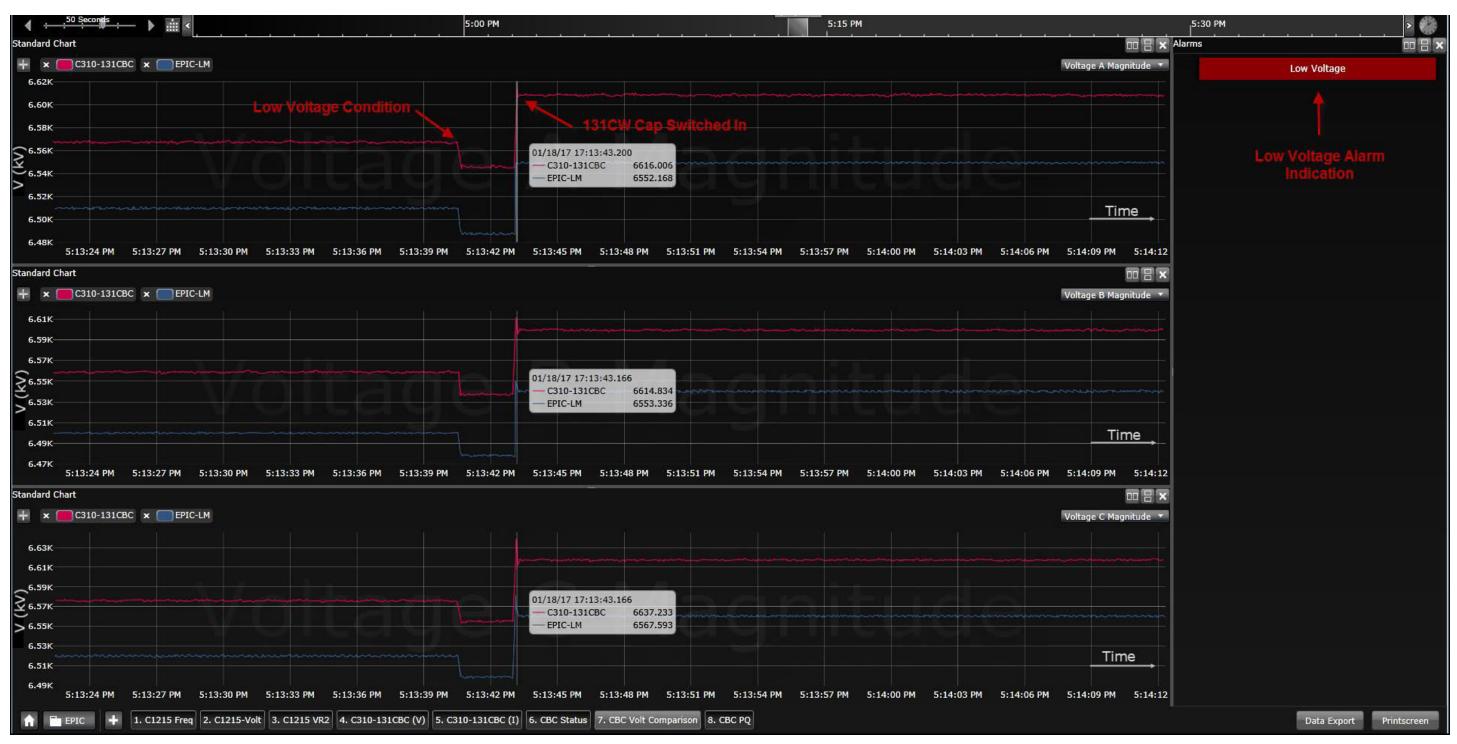

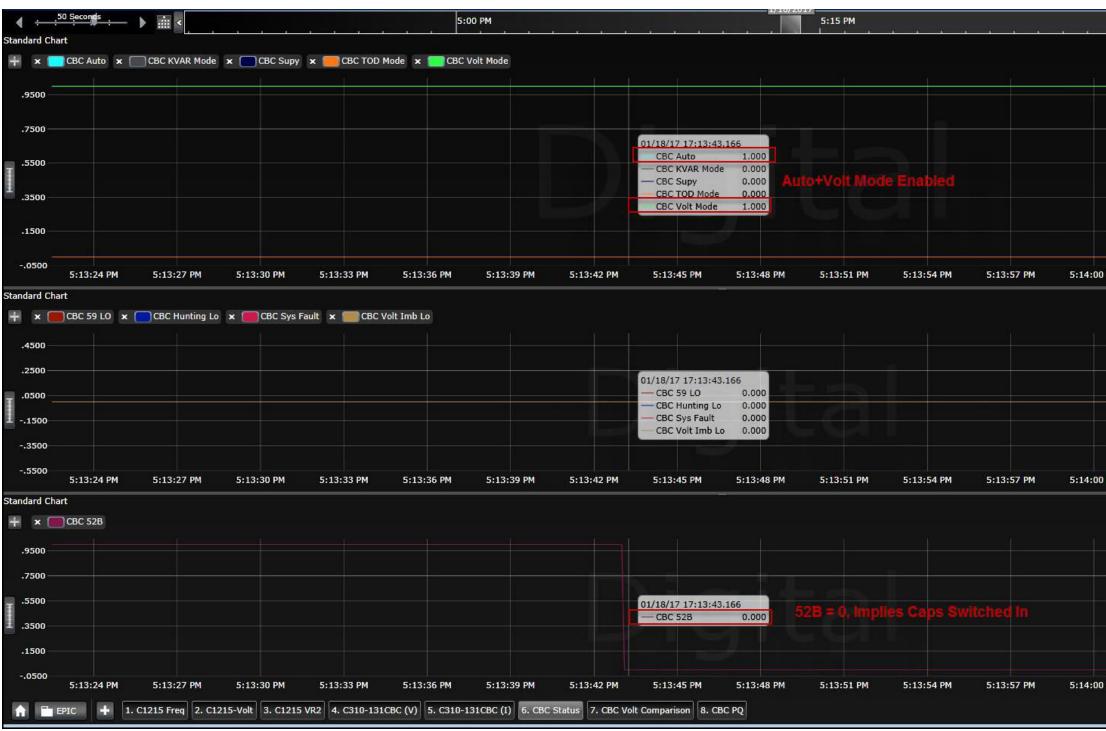

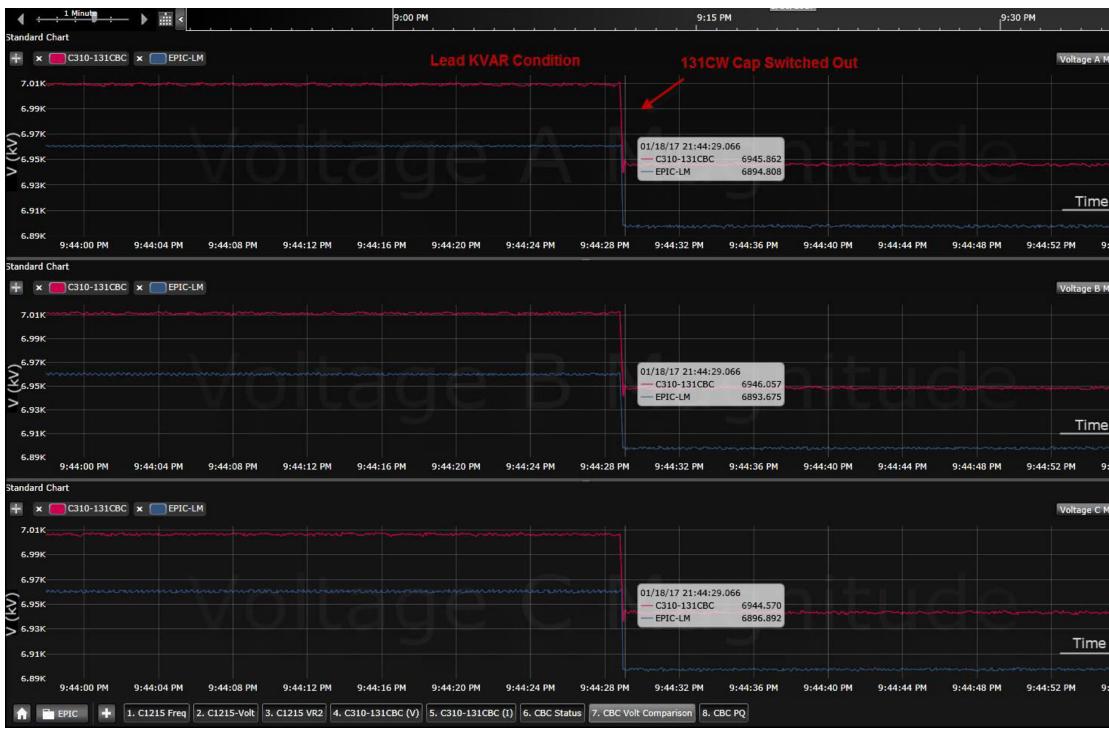

| 7.2.  | 3 Automatic Voltage Control Operation                            |  |

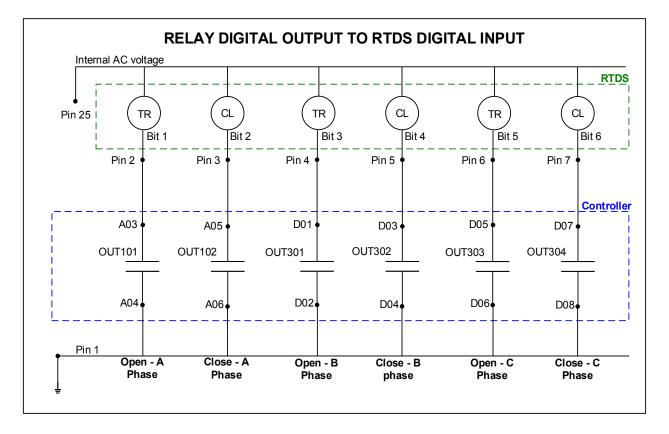

| 7.2.  | 4 Automatic KVAR Control Operation                               |  |

| 7.2.  | 5 Time-of-Day Operation                                          |  |

| 7.2.  | 6 Overvoltage Lockout                                            |  |

| 7.2.  | 7 Voltage Imbalance Lockout                                      |  |

| 7.2.  | 8 High-Current Condition                                         |  |

| 7.2.  | 9 Hunting Lockout                                                |  |

| 7.2.  | 10 Operations Counters                                           |  |

| 8  | Hig  | gh-Im | npedance Fault Detection                    | 154   |

|----|------|-------|---------------------------------------------|-------|

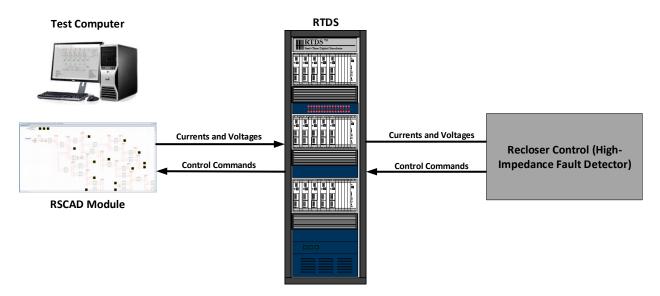

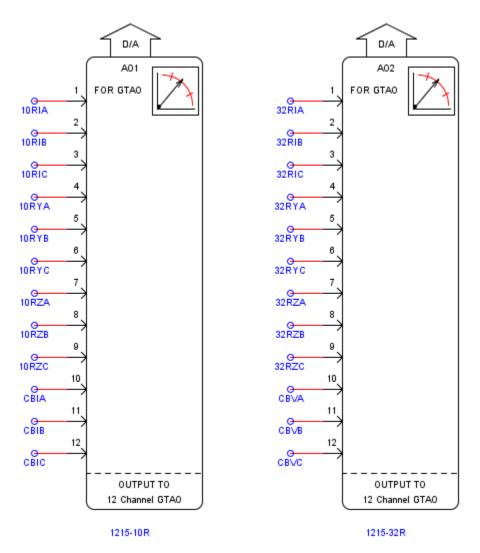

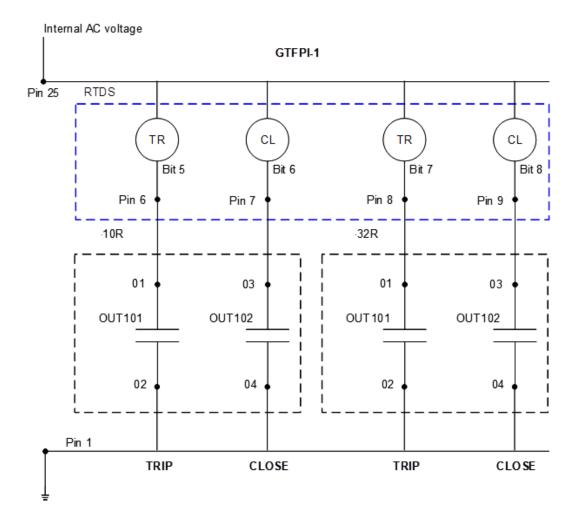

|    | 8.1  | Test  | Setup                                       | . 156 |

|    | 8.1. | 1     | RTDS Interface and I/O List                 | . 156 |

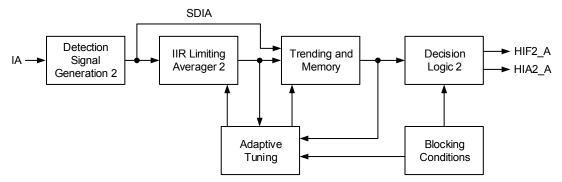

|    | 8.2  | HIF   | Overview                                    | . 159 |

|    | 8.2. | 1     | HIF Detection                               | . 159 |

|    | 8.3  | Test  | Procedure                                   | . 161 |

|    | 8.4  | Recl  | loser Control Settings                      | . 162 |

|    | 8.5  | Test  | Scenarios                                   | . 164 |

|    | 8.5. | 1     | Auto and Remote Toggle – From Local Control | . 164 |

|    | 8.5. | 2     | High-Impedance Fault Detection              | . 164 |

|    | 8.6  | Reco  | ommendation                                 | . 179 |

| 9  | Pov  | ver Q | Quality in Islands                          | 180   |

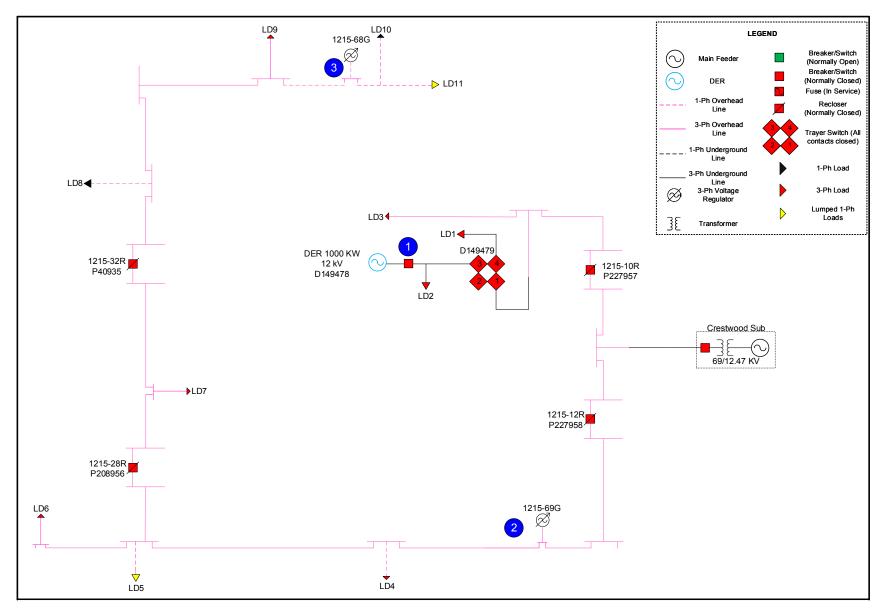

|    | 9.1  | Islar | nd Configurations                           | . 180 |

|    | 9.2  | Test  | Setup                                       | . 184 |

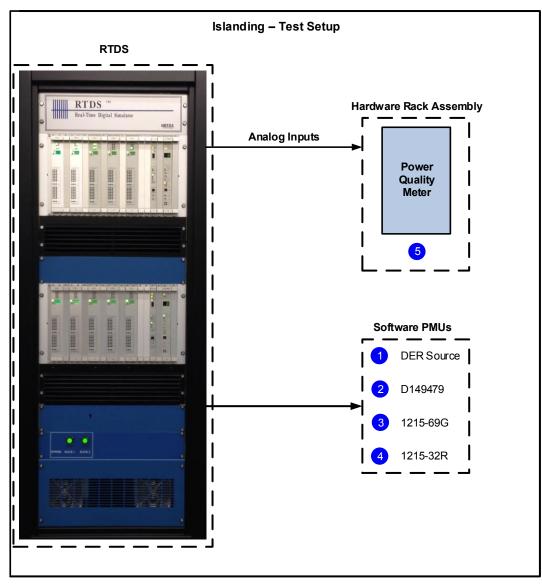

|    | 9.2. | 1     | Phasor Measurement Units                    | . 184 |

|    | 9.2. | 2     | RTDS and PMU Interface                      | . 186 |

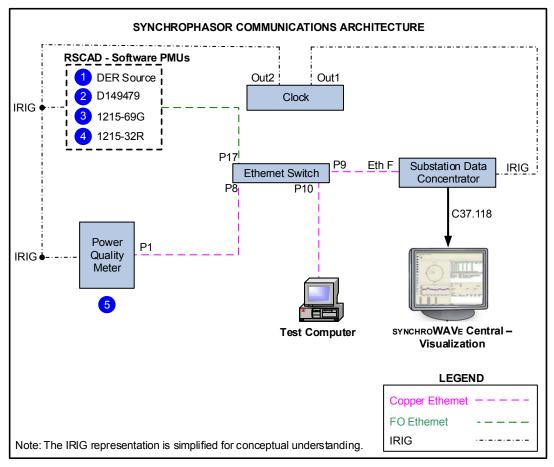

|    | 9.2. | 3     | PMU Communications Architecture             | . 186 |

|    | 9.3  | Test  | Procedure and Results                       | . 187 |

|    | 9.3. | 1     | Test 1                                      | . 187 |

|    | 9.3. | 2     | Test 2                                      | . 190 |

|    | 9.3. | 3     | Test 3                                      | . 191 |

| 1( | ) V  | oltag | ge Support Coodination Tests                | 193   |

|    | 10.1 | Circ  | uit Selection                               | . 193 |

|    | 10.2 | Test  | Setup                                       | . 195 |

|    | 10.2 | 2.1   | Distributed Energy Resource                 | . 195 |

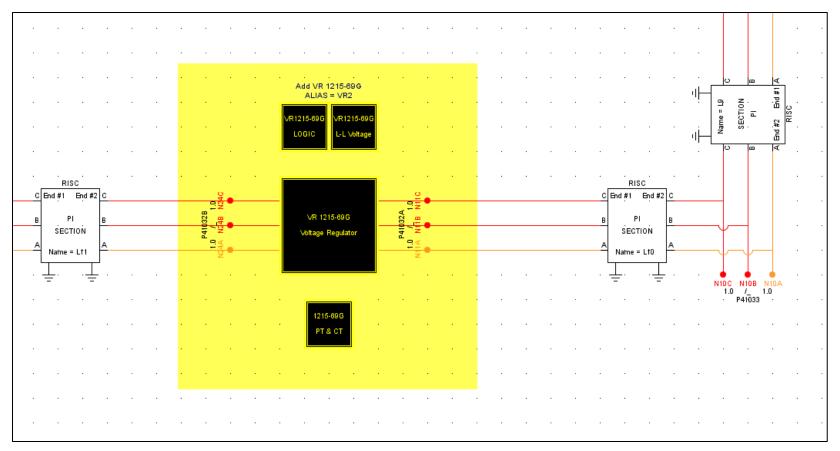

|    | 10.2 | 2.2   | Voltage Regulator                           | . 196 |

|    | 10.2 | 2.3   | Voltage Controller                          | . 196 |

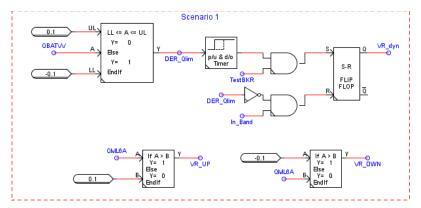

|    | 10.2 | 2.4   | RSCAD RunTime                               | . 198 |

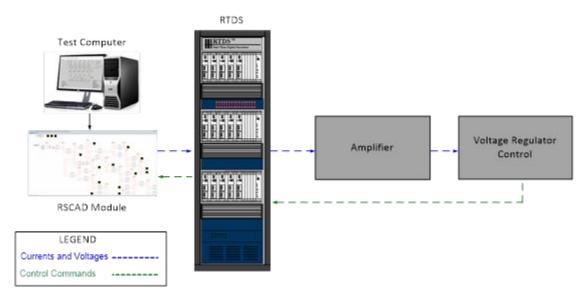

|    | 10.2 | 2.5   | Hardware Implementation                     | . 199 |

|    | 10.3 | Test  | Procedure                                   | . 199 |

|    | 10.3 | 3.1   | Load Switching                              | . 199 |

|    | 10.4 | Test  | Results                                     | . 201 |

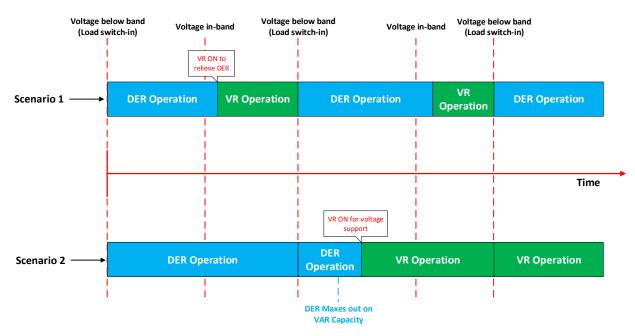

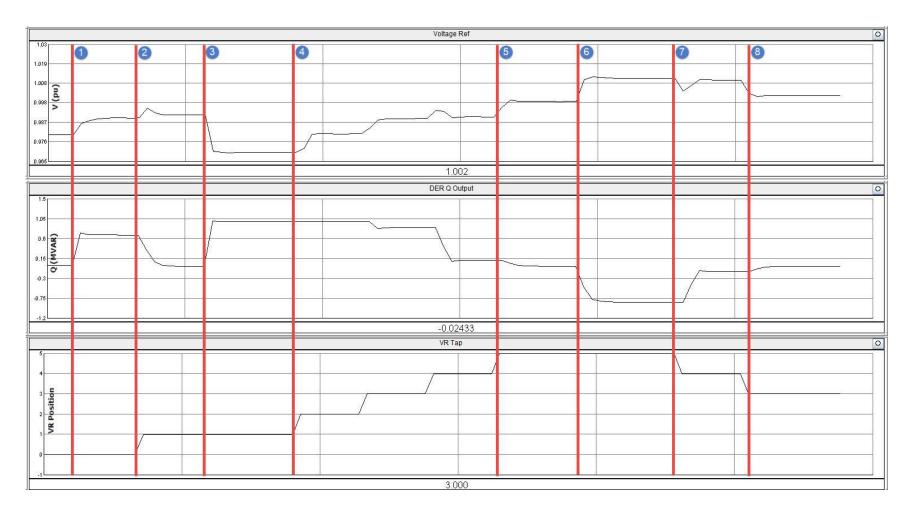

|    | 10.4 | 4.1   | Scenario 1                                  | . 201 |

|    | 10.4 | 4.2   | Scenario 2                                  | . 204 |

| 11    | Findings                                                       |     |

|-------|----------------------------------------------------------------|-----|

| 11.1  | Voltage Coordination Test Results Analysis                     |     |

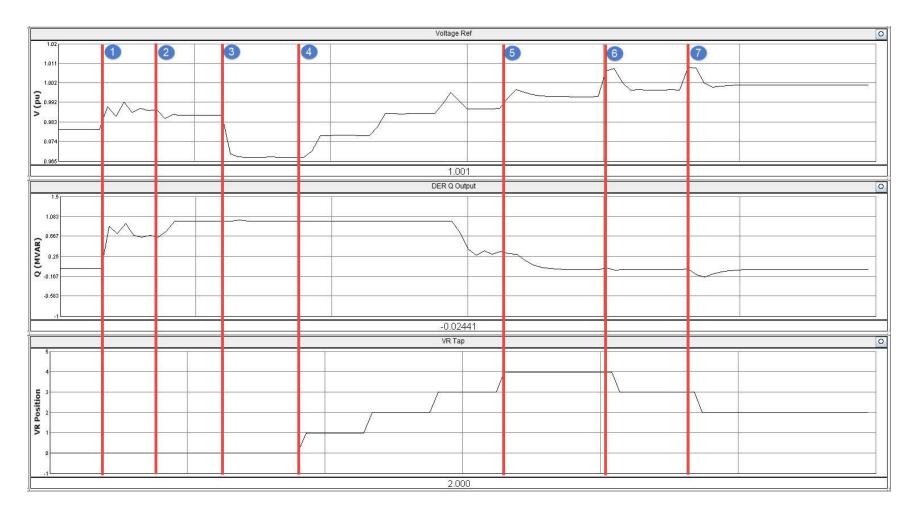

| 11.2  | 2 Voltage Regulator Location Analysis                          |     |

| 12    | Recommendations                                                |     |

| 12.1  | System Voltage Coordination – Advanced Control                 |     |

| 12.2  | 2 Downed Conductor Detection                                   |     |

| 12.3  | 3 Island Detection – Vector Shift Element                      |     |

| 12    | 2.3.1 Vector Shift Element Logic                               |     |

| 12.4  | Island Detection – Fast Rate-of-Change-of-Frequency Protection |     |

| 12.5  | 5 Fast Decoupling Schemes                                      |     |

| 12    | 2.5.1 Local Decoupling Protection Scheme                       |     |

| 12    | 2.5.2 Synchrophasor-Based Decoupling Protection                |     |

|       | 12.5.2.1 Synchrophasor Protocol                                |     |

|       | 12.5.2.2 Synchrophasor-Based Decoupling Protection             |     |

| 12.6  | 5 Power Quality Monitoring                                     |     |

| 12    | 2.6.1 Voltage Sag, Swell, and Interruption                     |     |

| 12    | 2.6.2 Harmonics                                                |     |

| 12    | 2.6.3 Unbalance                                                |     |

| 13    | Technology Transfer Plan                                       |     |

| 13.1  | Introduction                                                   |     |

| 13.2  | 2 Procedure for Commercial Implementation                      |     |

| 13    | 3.2.1 Design and Review                                        |     |

| 13    | 3.2.2 In-house Testing and Validation                          |     |

| 13    | 3.2.3 Field Implementation and Monitoring                      |     |

| 13.3  | 3 Challenges                                                   |     |

| 13.4  | Resources                                                      |     |

| 13.5  | 5 Conclusion                                                   |     |

| 14    | Overall Project Conclusions                                    | 222 |

| 15    | Metrics And Value Proposition                                  | 223 |

| 15.1  | Project Metrics                                                |     |

| 15.2  | 2 Value Proposition: Primary And Secondary Guiding Principles  |     |

| 16    | References                                                     |     |

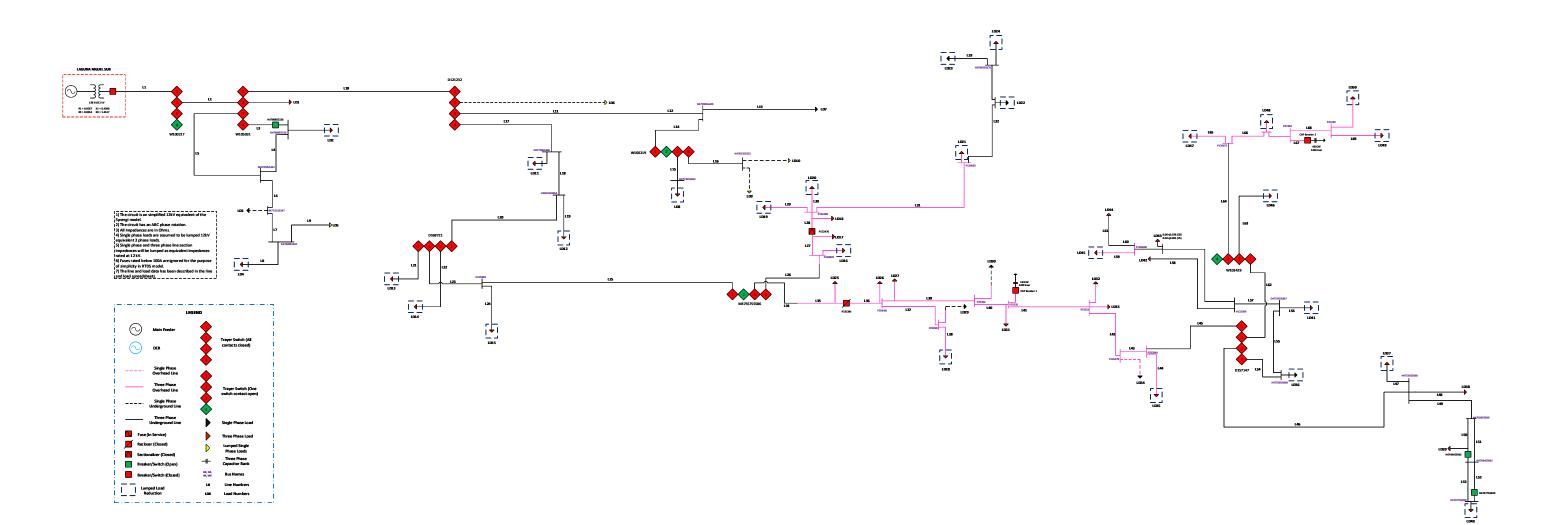

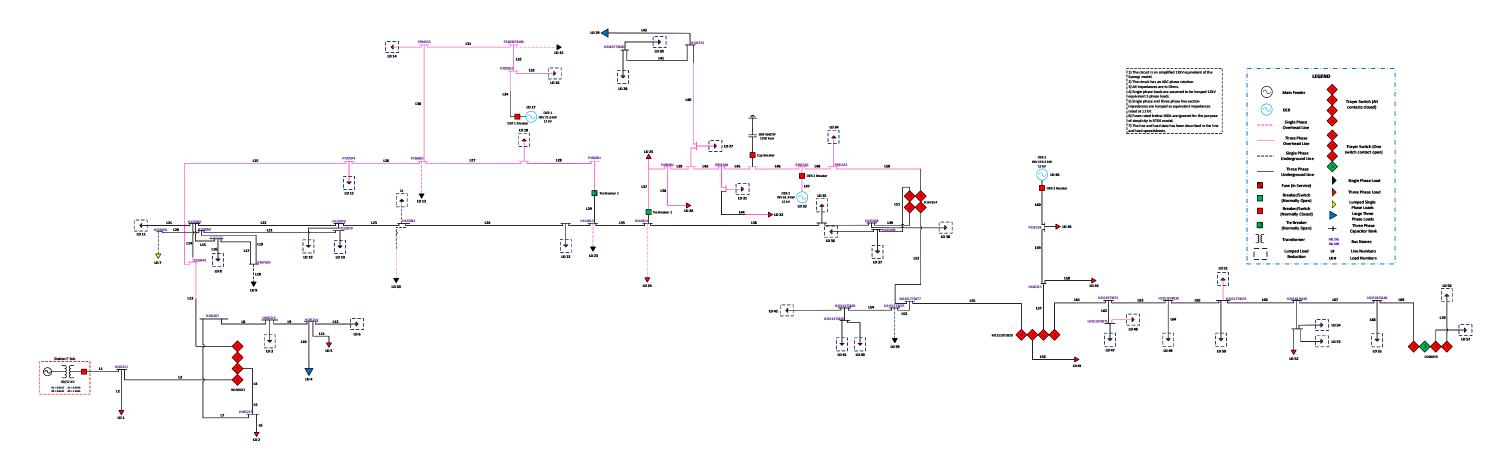

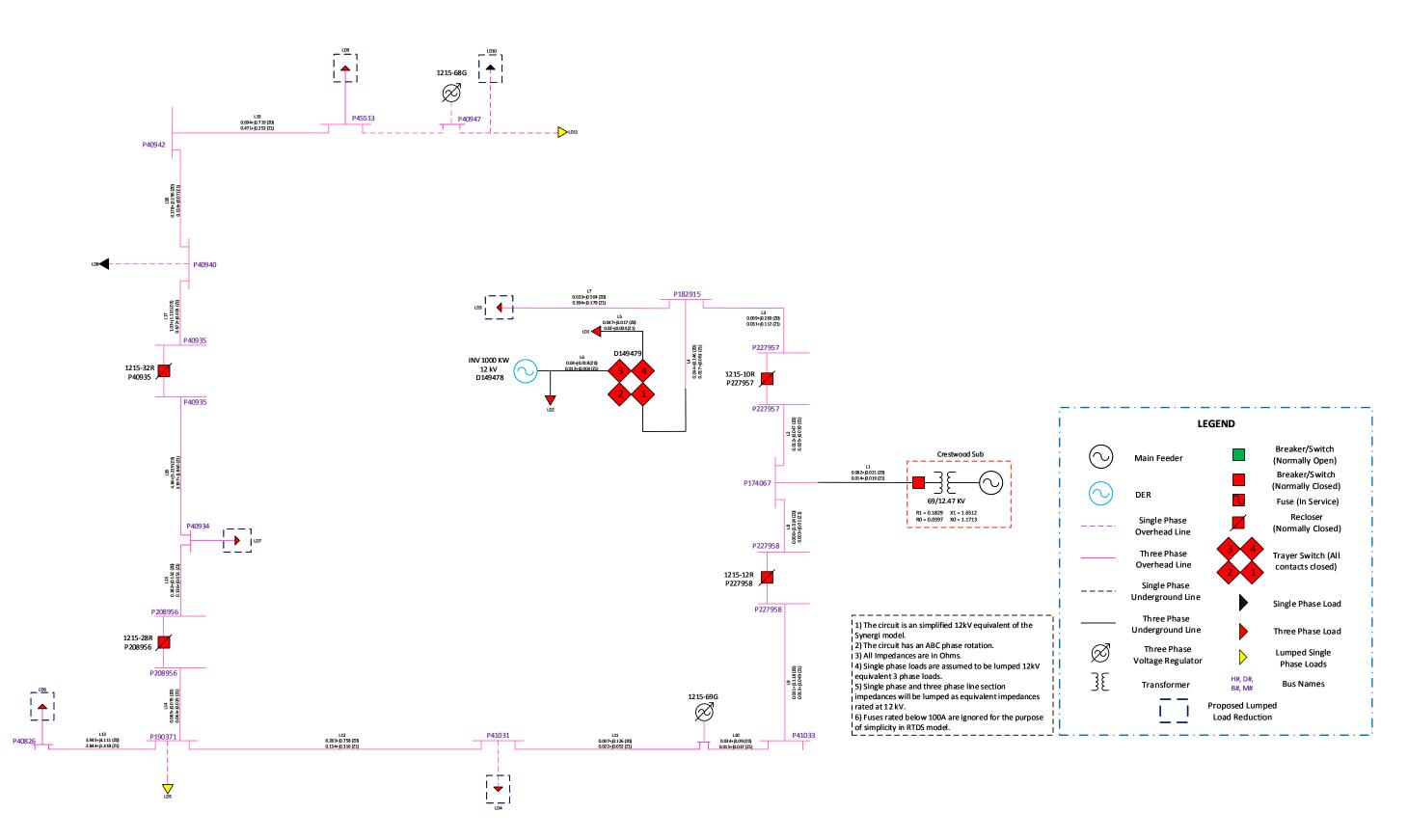

| Apper | ndix A Circuit One-Line Diagram                                |     |

| Apper | ndix B Load Profile                                            |     |

| Appendix C | Voltage Regulator Control Settings | . 245 |

|------------|------------------------------------|-------|

| Appendix D | Recloser Settings Sheet            | . 260 |

# **List of Figures**

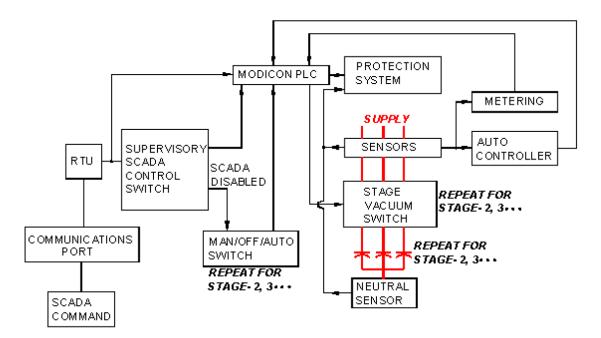

| Figure 3.1: DVR General Configuration                                                   | 9  |

|-----------------------------------------------------------------------------------------|----|

| Figure 3.2: Protection Mode                                                             | 9  |

| Figure 3.3: Standby Mode                                                                | 10 |

| Figure 3.4: Block Diagram of a SCADA-Controlled Metal-Enclosed Automatic Capacitor Bank | 13 |

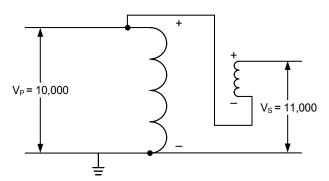

| Figure 3.5: Step-Up Autotransformer (Boost Mode)                                        | 16 |

| Figure 3.6: Step-Down Autotransformer (Buck Mode)                                       | 17 |

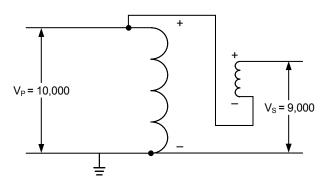

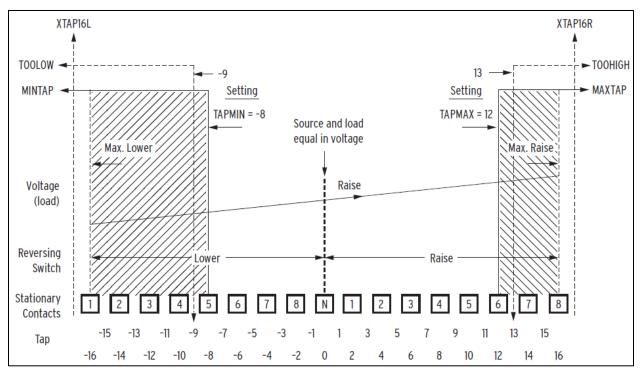

| Figure 3.7: Connection of 32-Step and 4-Step Regulators                                 | 17 |

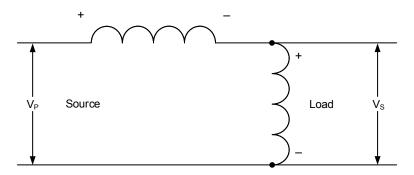

| Figure 3.8: Microprocessor-Based Transformer Monitor I/O and Communications             | 26 |

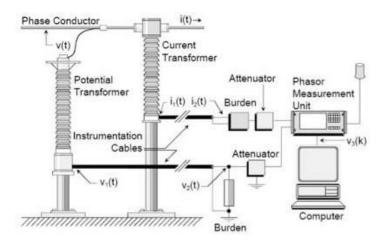

| Figure 3.9: PMU Used to Monitor Power Flowing Through Electrical Grid                   |    |

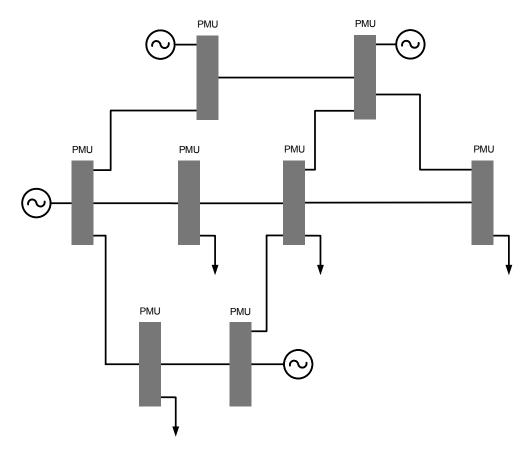

| Figure 3.10: PMUs Installed at Every Substation Monitoring the Power Grid               | 29 |

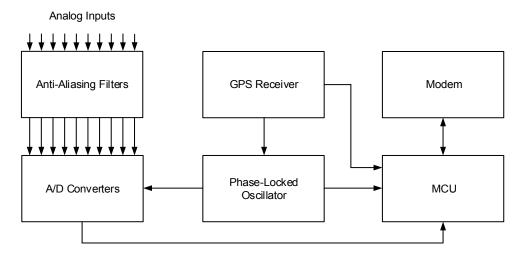

| Figure 3.11: Block Diagram of a PMU                                                     | 30 |

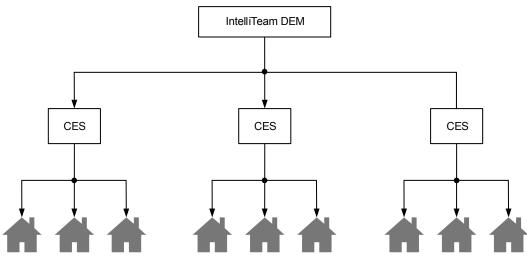

| Figure 3.12: Simplified Representation of DEM Systems Supporting CES Fleet Systems      |    |

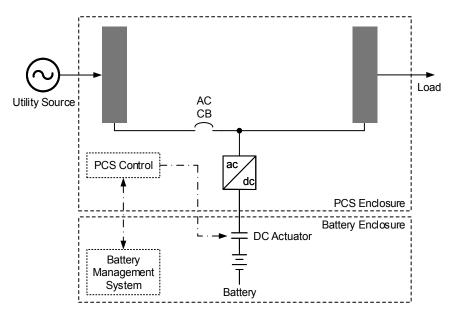

| Figure 3.13: Simplified Circuit Representation of CES Units                             | 40 |

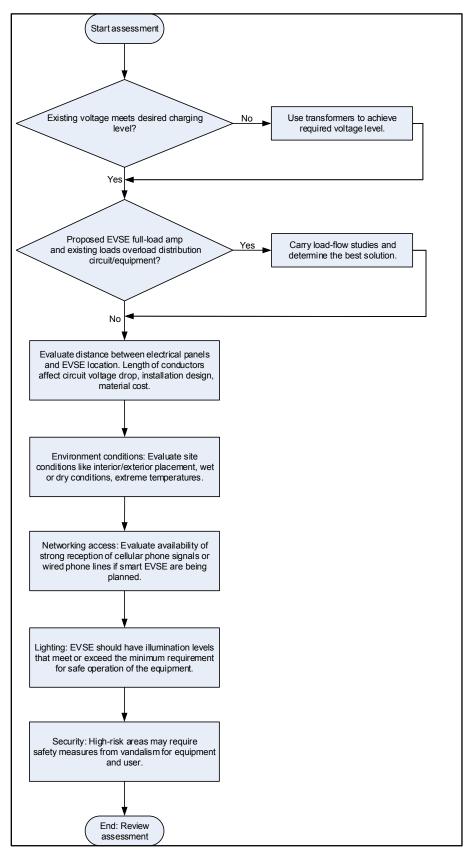

| Figure 3.14: Electrical Assessment Prior to EVSE Installation                           | 43 |

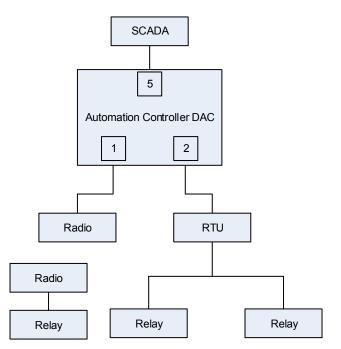

| Figure 4.1: Example of ADAC Implementation                                              | 48 |

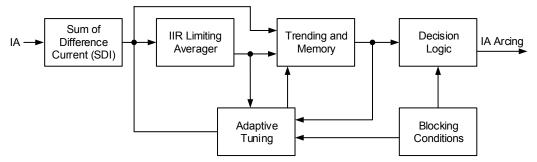

| Figure 4.2: Block Diagram of HIF Detection (Nonharmonic)                                | 59 |

| Figure 4.3: Balance Equation Schematic                                                  | 61 |

| Figure 5.1: Line Impedance Conversion From Synergi to RSCAD                             | 64 |

| Figure 5.2: Load Impedance Conversion From Synergi to RSCAD                             | 66 |

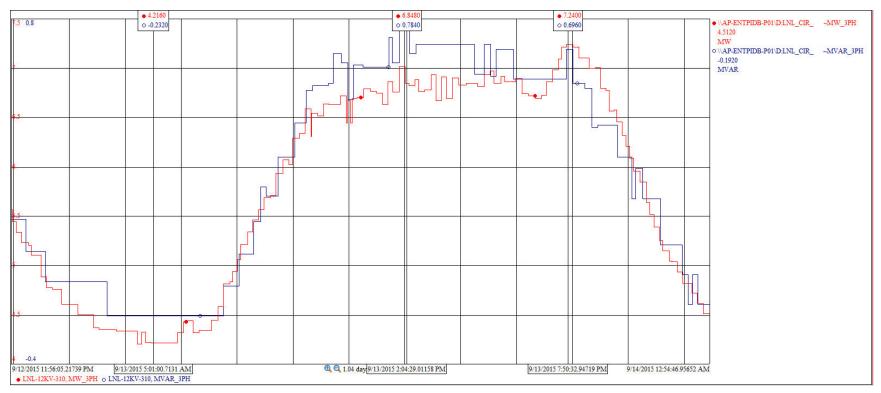

| Figure 5.3: Coastal-Residential Test Circuit – 24-Hour Field Load Profile               | 68 |

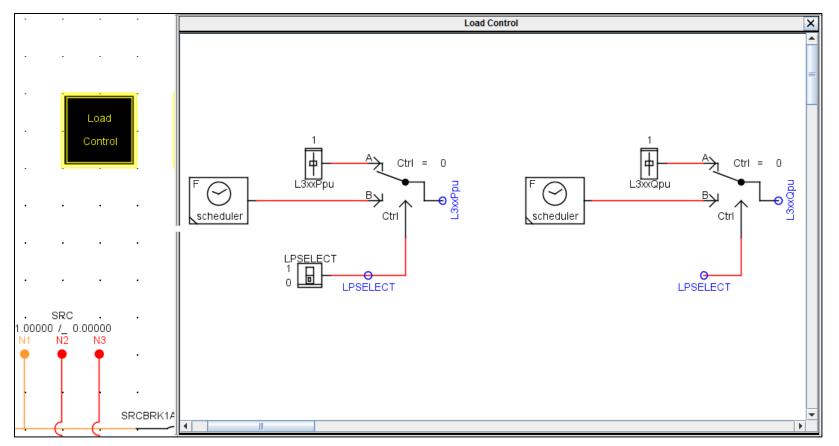

| Figure 5.4: RSCAD Load Control                                                          | 69 |

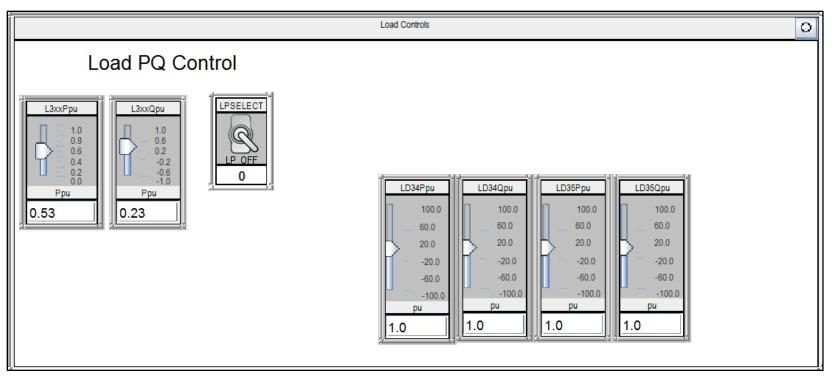

| Figure 5.5: RSCAD Load Control HMI                                                      | 70 |

| Figure 6.1: Voltage Regulator Control Test Setup                                        | 72 |

| Figure 6.2: RTDS to Vendor B Amplifier Interface                                        | 75 |

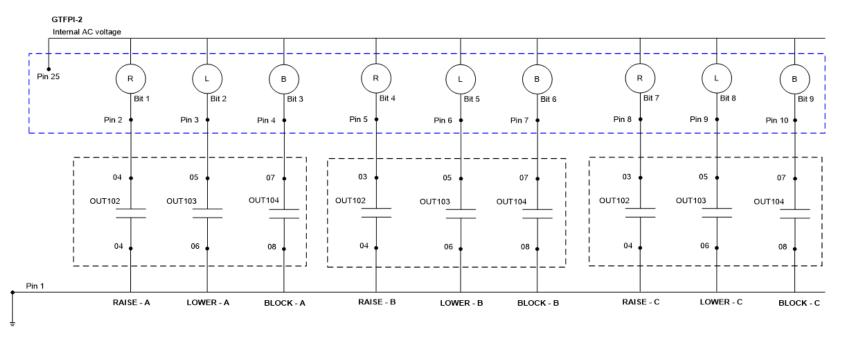

| Figure 6.3: Raise, Lower, and Block Digital Input Wiring                                | 76 |

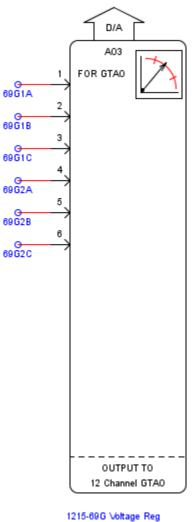

| Figure 6.4: Voltage Regulator External Connection Diagram                               | 77 |

| Figure 6.5: Voltage Regulator Internal Connection Diagram                               | 78 |

| Figure 6.6: Voltage Profile Plot of a Continual Raise Operation                         | 79 |

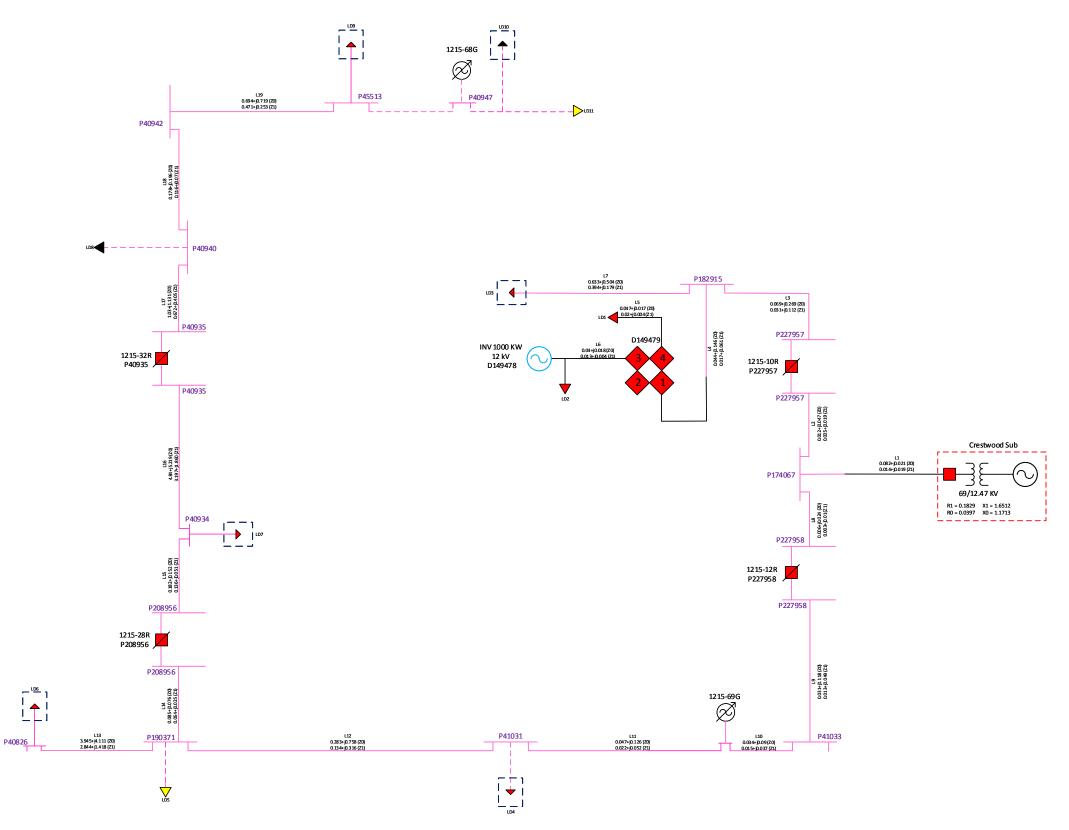

| Figure 6.7: Simplified One-Line Drawing of Desert-Rural Test Circuit                    | 82 |

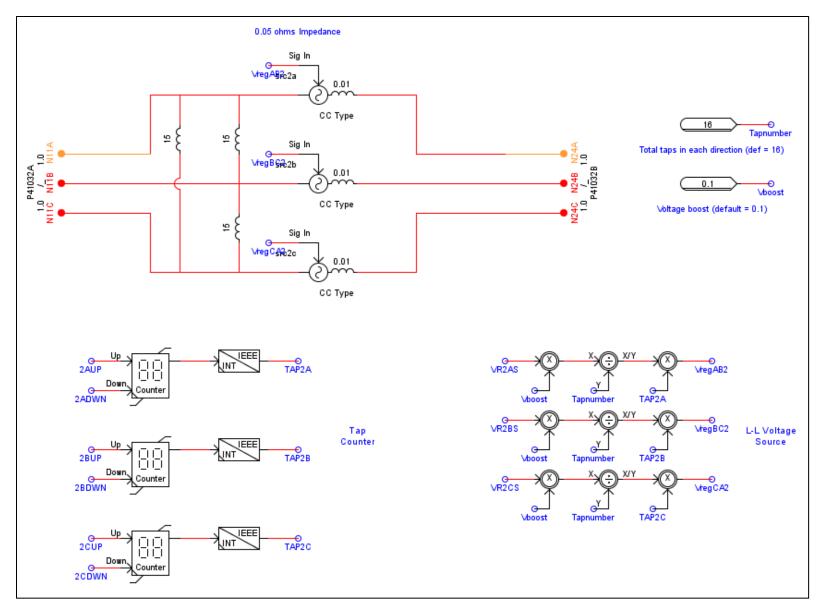

| Figure 6.8: Voltage Regulator RTDS Block                                                | 84 |

| Figure 6.9: Voltage Regulator Internal Logic                                            | 85 |

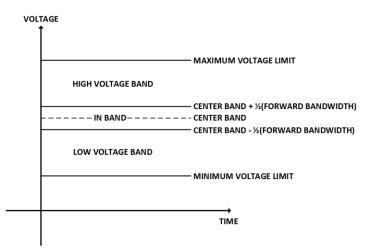

| Figure 6.10: Voltage Regulator Voltage Band Setting                                     | 87 |

| Figure 6.11: Test Scenario 3.7.1. Phase A Voltage Regulator SER                                           | 89    |

|-----------------------------------------------------------------------------------------------------------|-------|

| Figure 6.12: Test Scenario 3.7.1. Phase B Voltage Regulator SER                                           | 89    |

| Figure 6.13: Test Scenario 3.7.1. Phase C Voltage Regulator SER                                           | 89    |

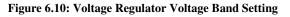

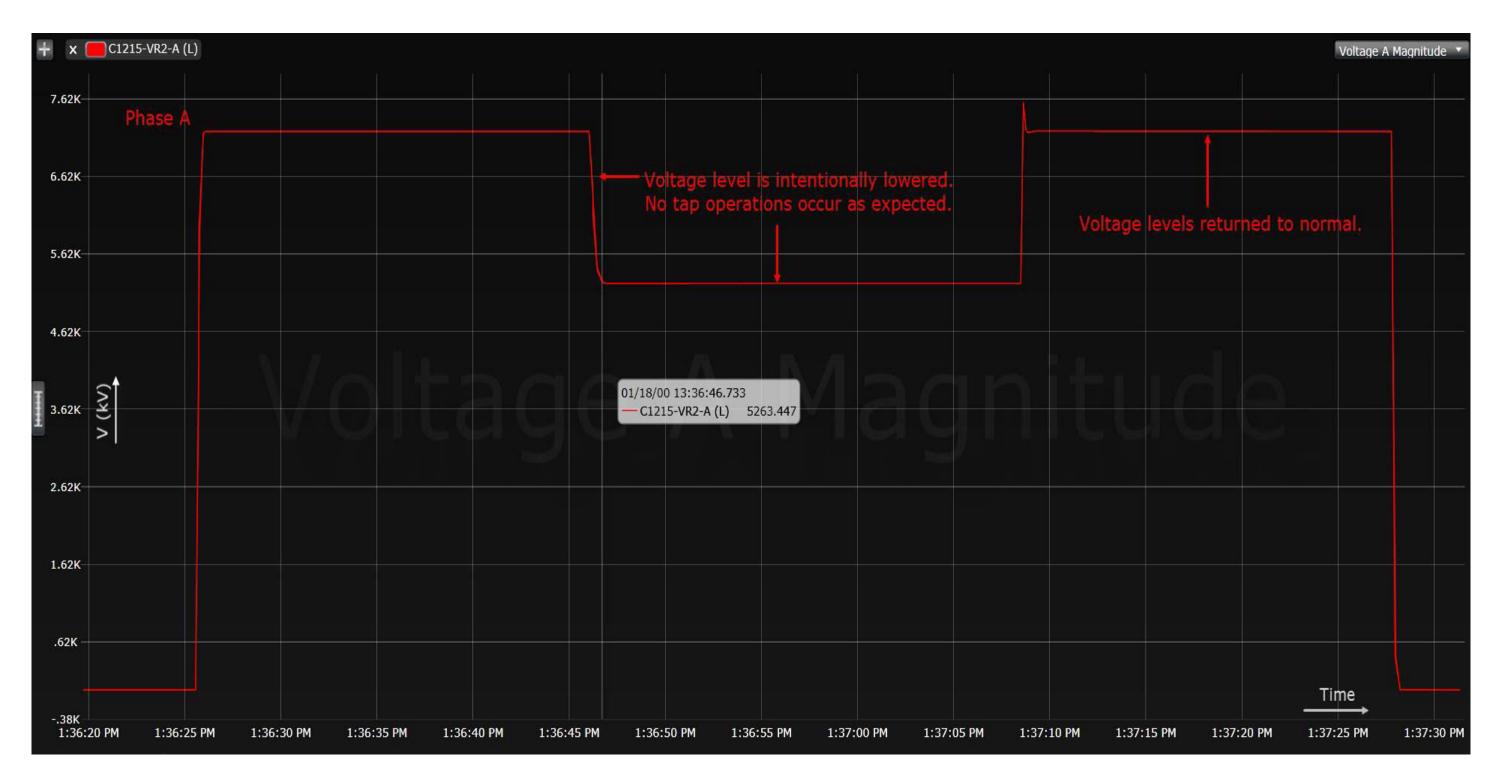

| Figure 6.14: Test Scenario 3.7.2. Phase A Voltage Regulator Output Voltage Waveform                       | 92    |

| Figure 6.15: Test Scenario 3.7.2. Phase A Voltage Regulator SER                                           | 93    |

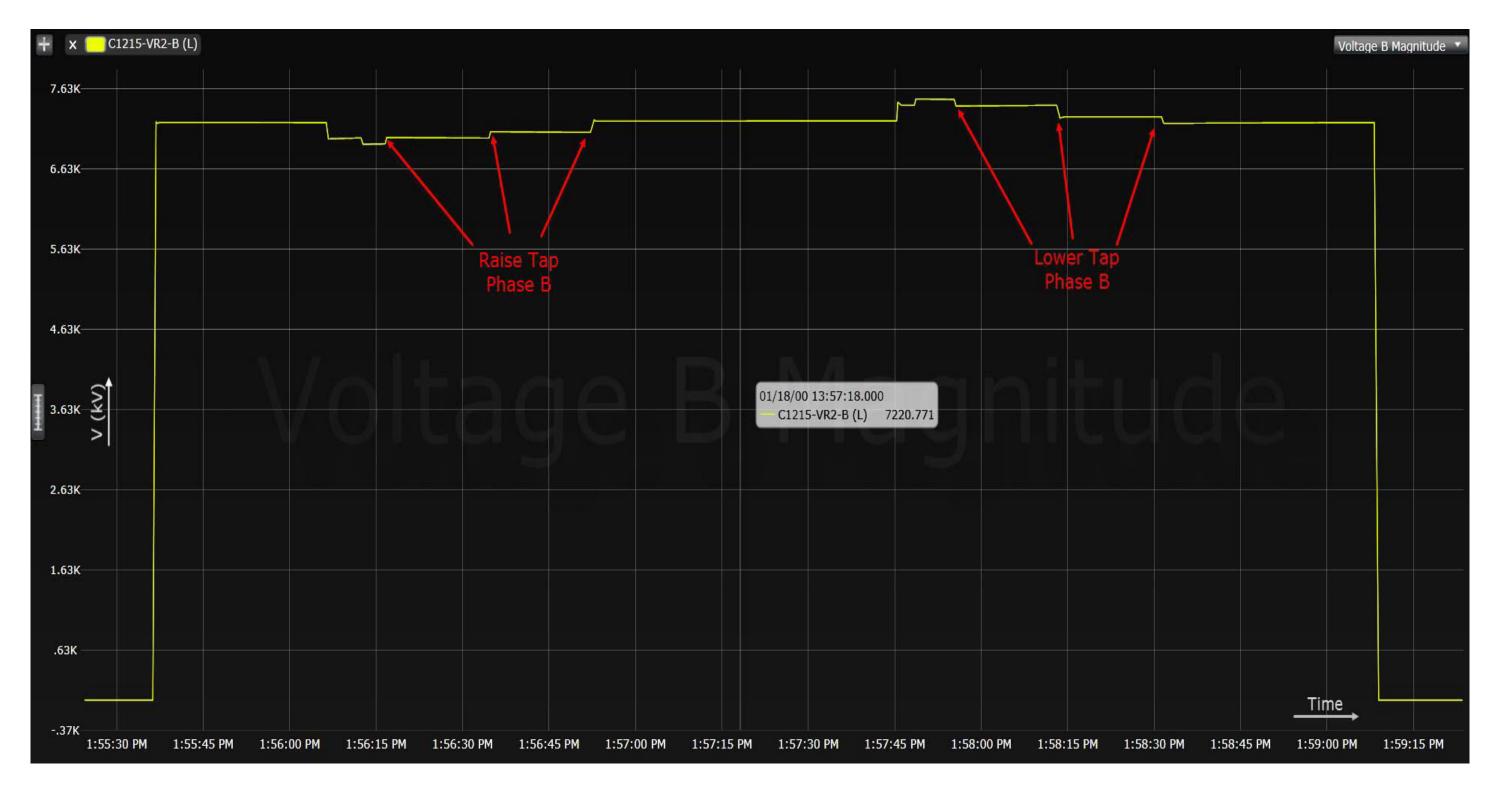

| Figure 6.16: Test Scenario 3.7.2. Phase B Voltage Regulator Output Voltage Waveform                       | 94    |

| Figure 6.17: Test Scenario 3.7.2. Phase B Voltage Regulator SER                                           | 95    |

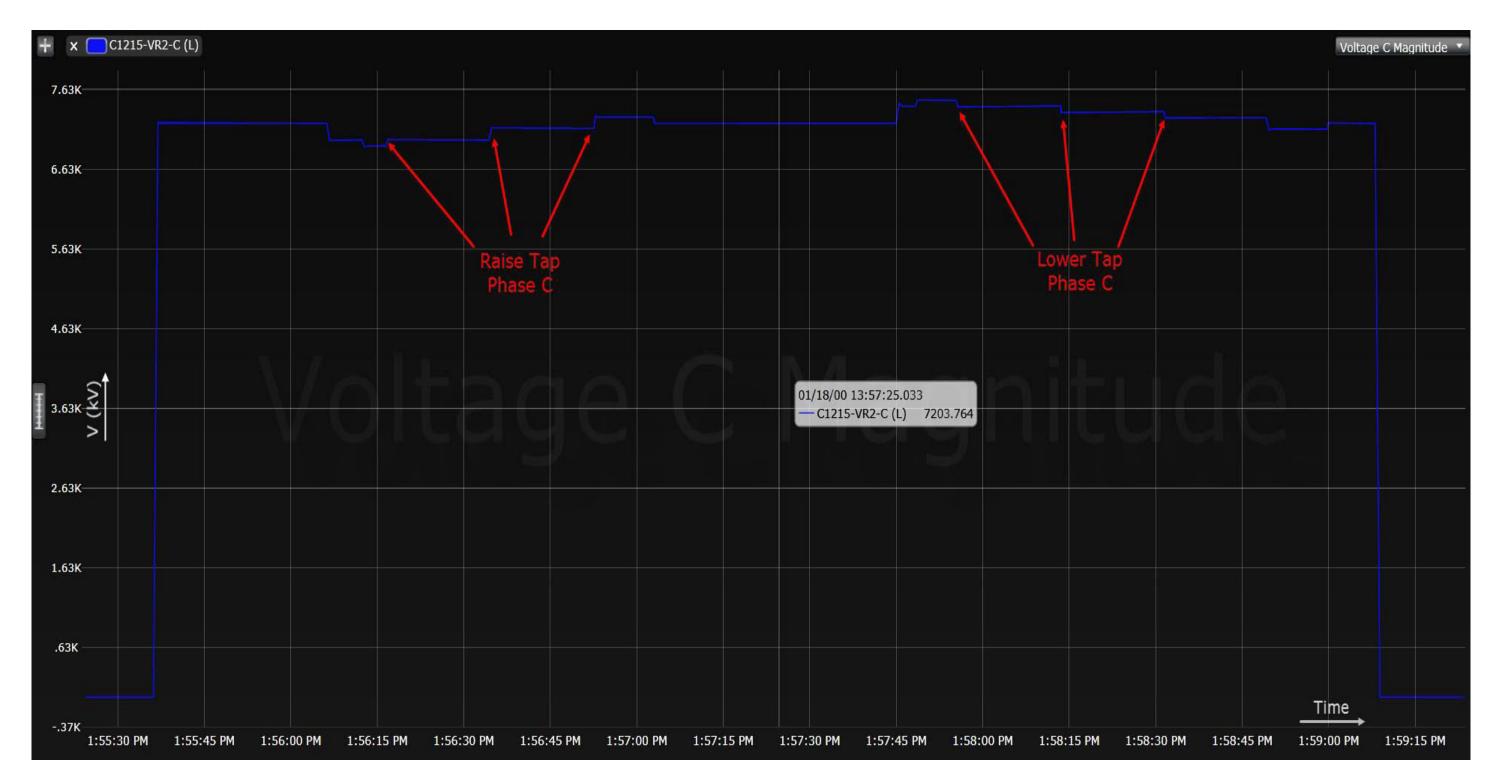

| Figure 6.18: Test Scenario 3.7.2. Phase C Voltage Regulator Output Voltage Waveform                       | 96    |

| Figure 6.19: Test Scenario 3.7.2. Phase C Voltage Regulator SER                                           | 97    |

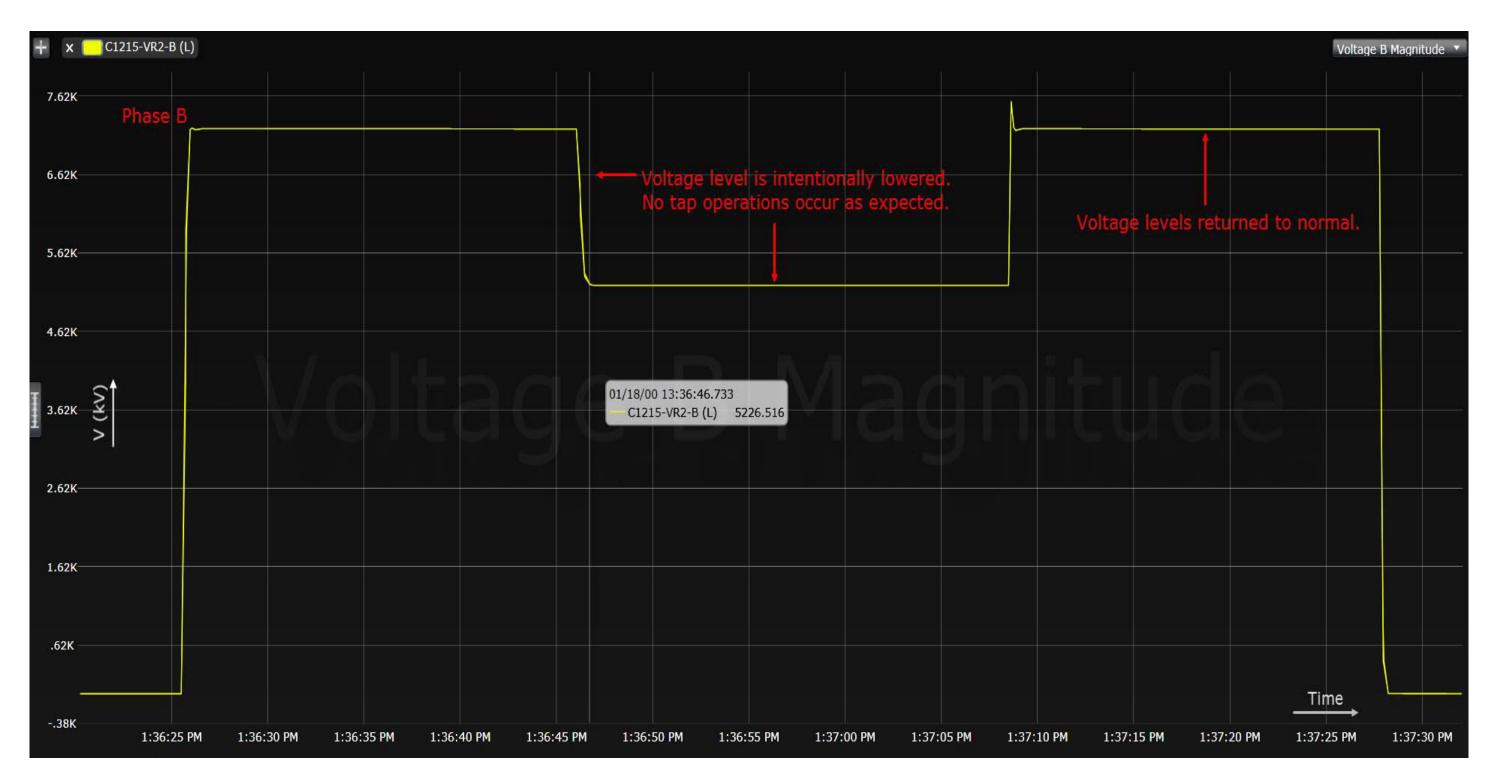

| Figure 6.20: Test Scenario 3.7.3. Phase A Voltage Regulator Output Voltage Waveform                       | 99    |

| Figure 6.21: Test Scenario 3.7.3. Phase A Voltage Regulator SER                                           | 100   |

| Figure 6.22: Test Scenario 3.7.3. Phase B Voltage Regulator Output Voltage Waveform                       | 101   |

| Figure 6.23: Test Scenario 3.7.3. Phase B Voltage Regulator SER                                           | 102   |

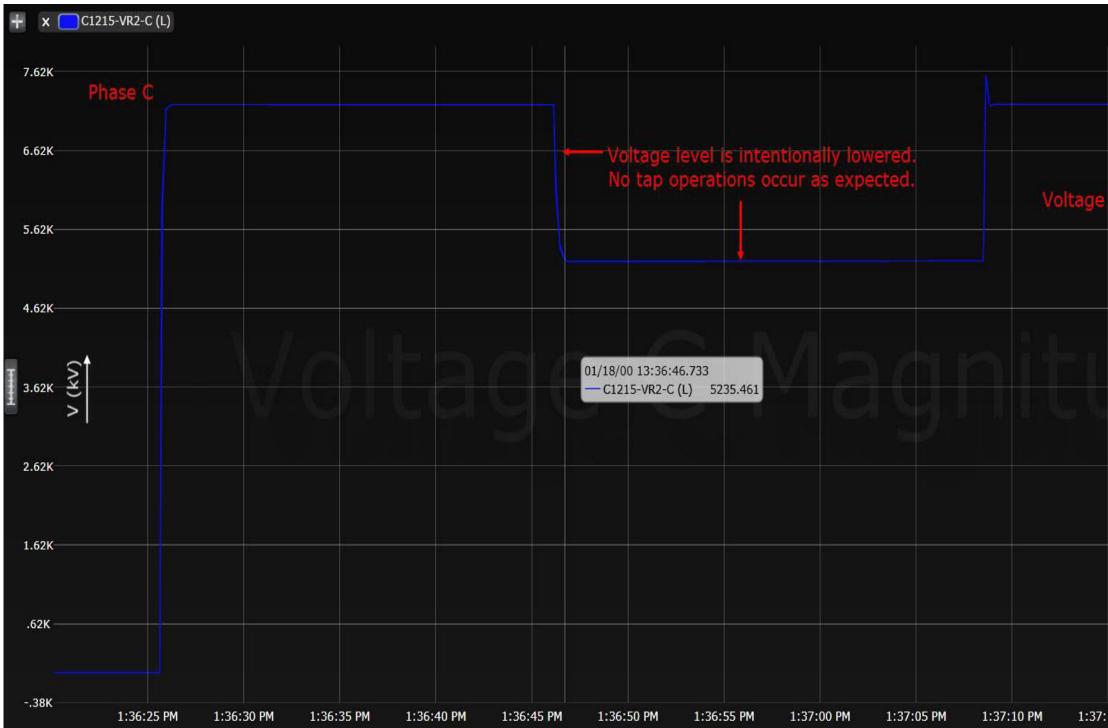

| Figure 6.24: Test Scenario 3.7.3. Phase C Voltage Regulator Output Voltage Waveform                       | 103   |

| Figure 6.25: Test Scenario 3.7.3. Phase C Voltage Regulator SER                                           | 104   |

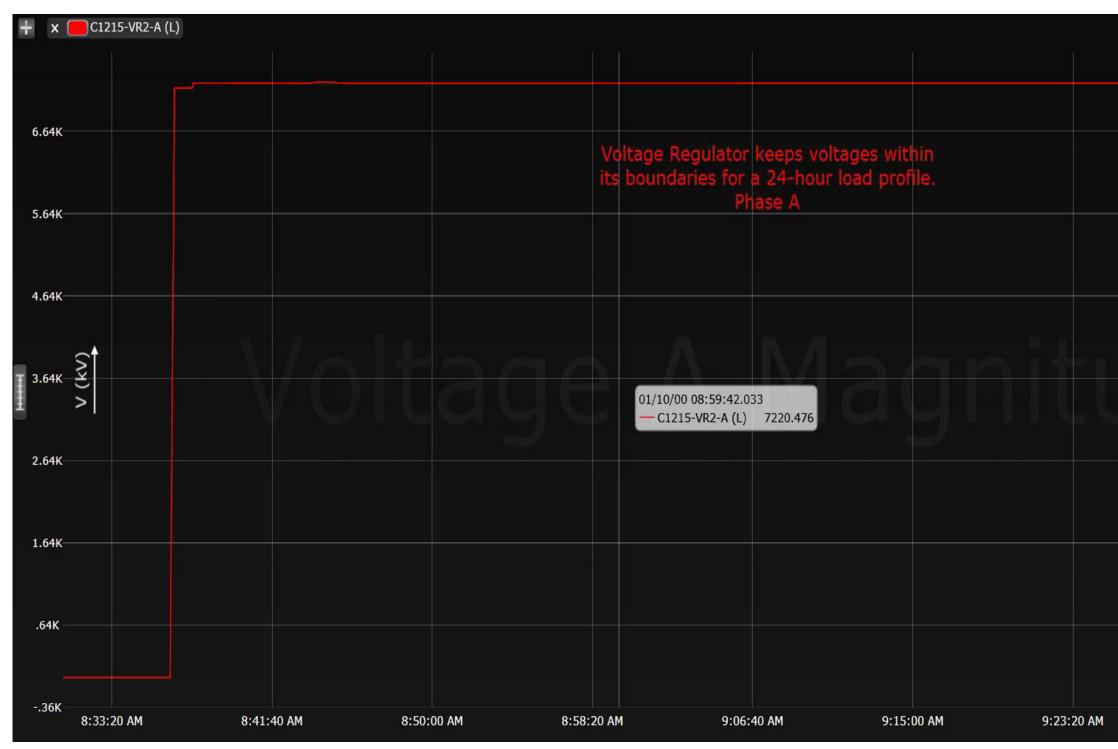

| Figure 6.26: Test Scenario 3.7.4. Phase A Voltage Regulator Output Voltage Waveform - Normal Load Profile | 106   |

| Figure 6.27: Test Scenario 3.7.4. Phase A Voltage Regulator SER – Normal Load Profile                     | 107   |

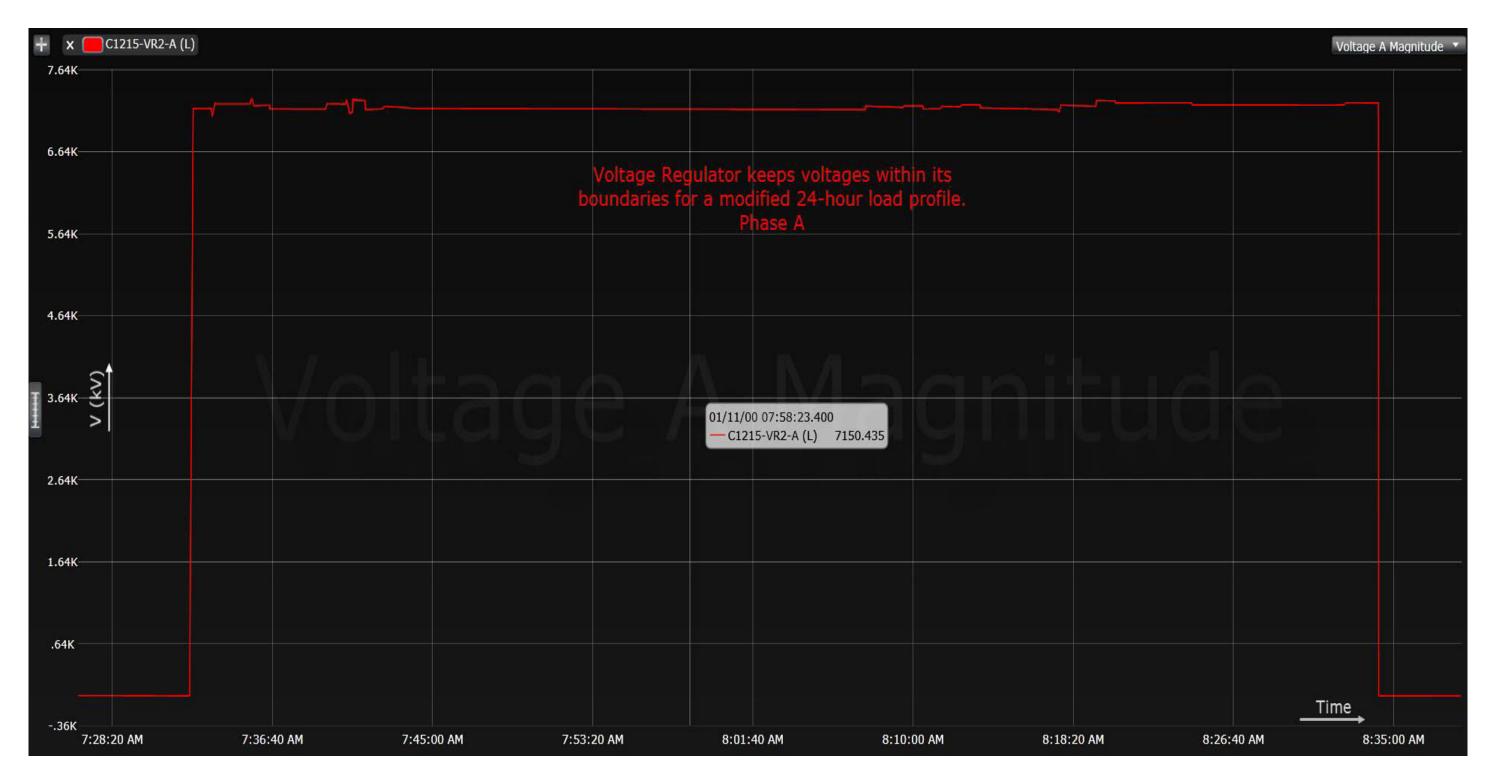

| Figure 6.28: Test Scenario 3.7.4. Phase A Voltage Regulator Output Voltage Waveform - Modified Load Profi | le108 |

| Figure 6.29: Test Scenario 3.7.4. Phase A Voltage Regulator SER – Modified Load Profile                   | 109   |

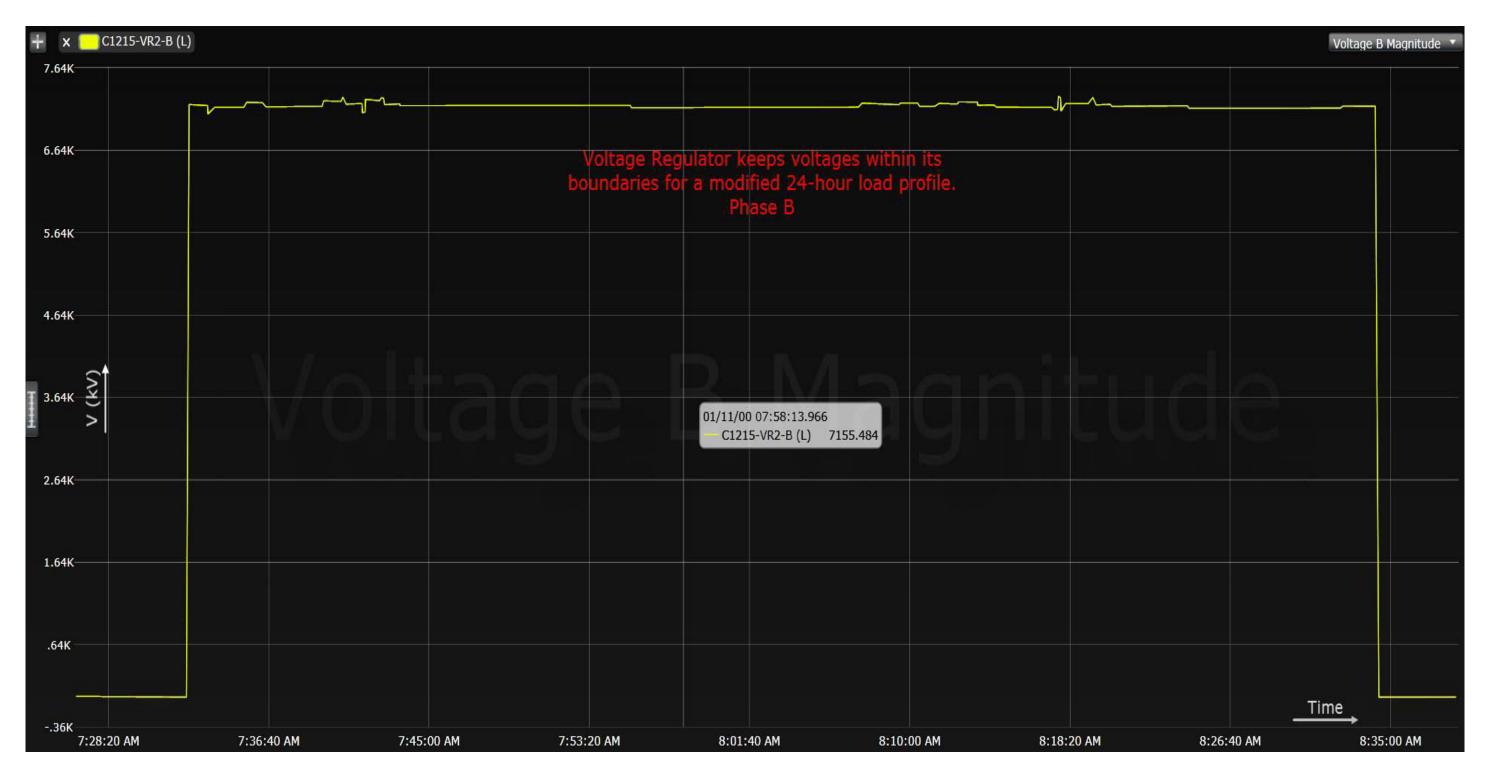

| Figure 6.30: Test Scenario 3.7.4. Phase B Voltage Regulator Output Voltage Waveform - Modified Load Profi | le110 |

| Figure 6.31: Test Scenario 3.7.4. Phase B Voltage Regulator SER – Modified Load Profile                   | 111   |

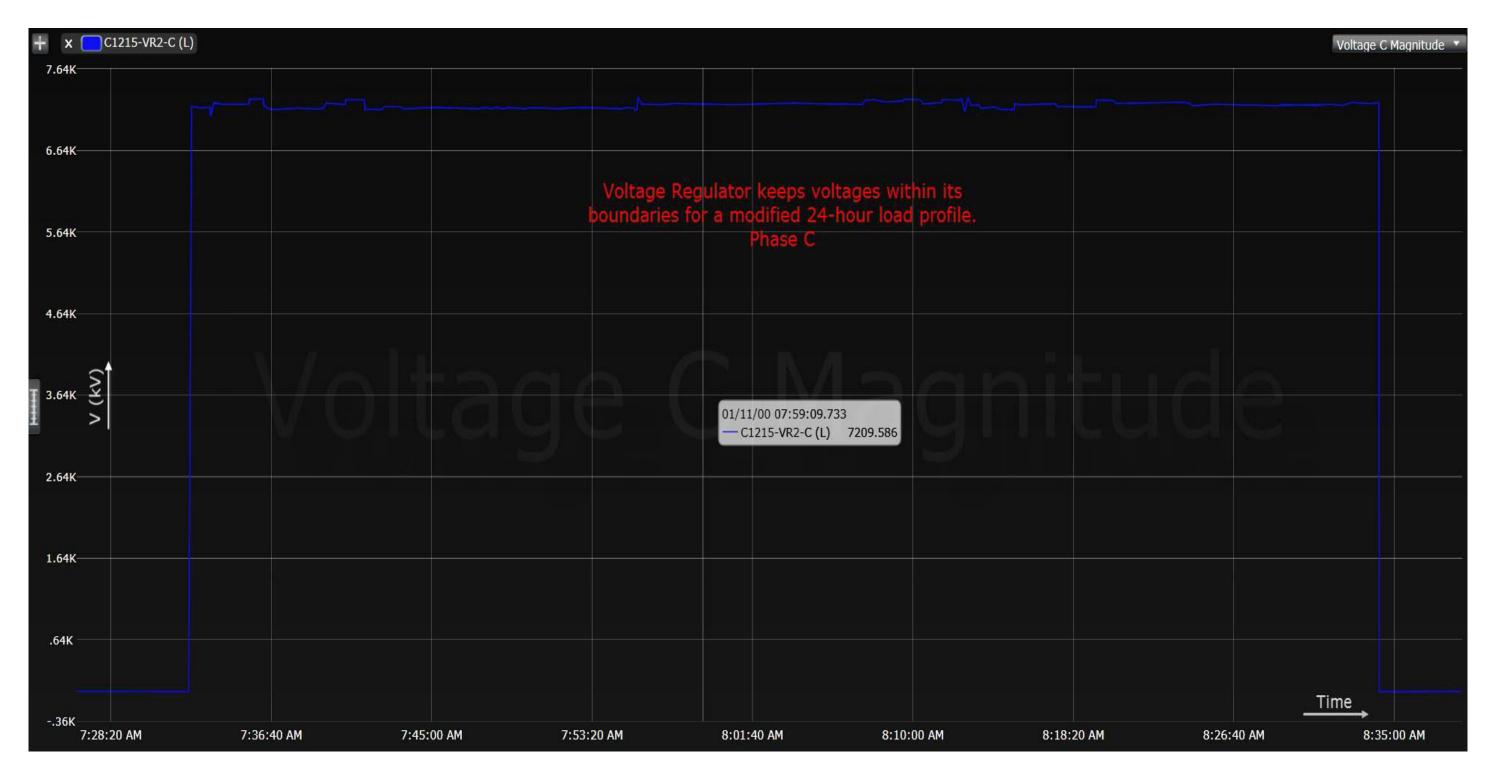

| Figure 6.32: Test Scenario 3.7.4. Phase C Voltage Regulator Output Voltage Waveform - Modified Load Profi | le112 |

| Figure 6.33: Test Scenario 3.7.4. Phase C Voltage Regulator SER – Modified Load Profile                   | 113   |

| Figure 7.1: Controller Front-Panel Layout                                                                 | 115   |

| Figure 7.2: Controller Low-Level Test Interface J2                                                        | 115   |

| Figure 7.3: CBC – Test Setup                                                                              | 116   |

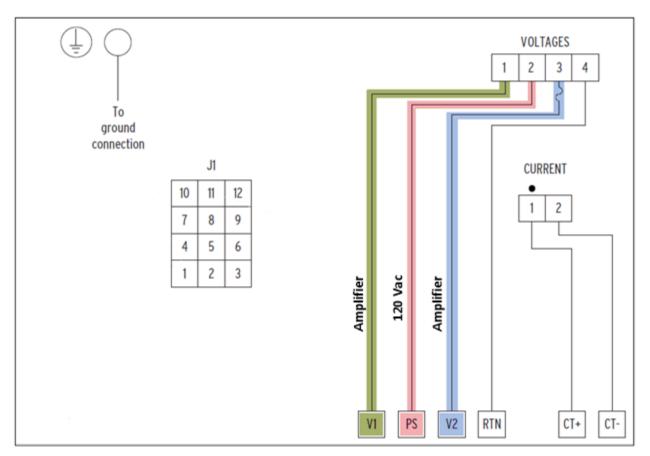

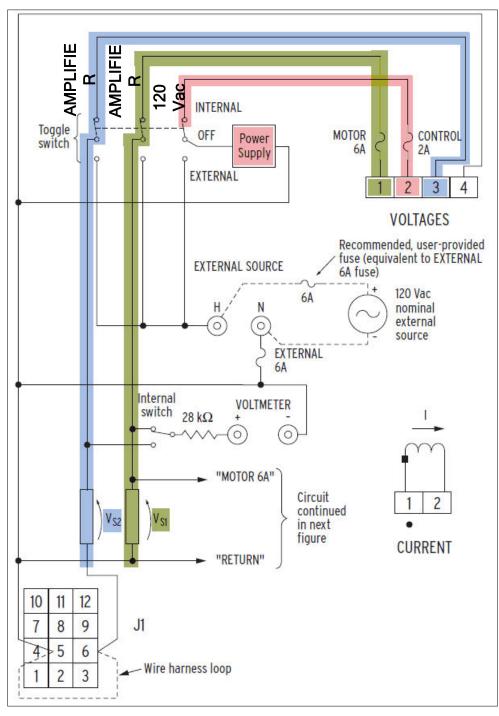

| Figure 7.4: RTDS and Controller Interface – Analog Inputs                                                 | 117   |

| Figure 7.5: RTDS and Controller Interface – Digital Inputs                                                | 118   |

| Figure 7.6: RTDS and Controller Interface – Digital Outputs                                               | 118   |

| Figure 7.7: CBC KVAR Operations – Quadrants I and IV                                                      | 120   |

| Figure 7.8: CBC SUPY Mode Enabled                                                                         | 124   |

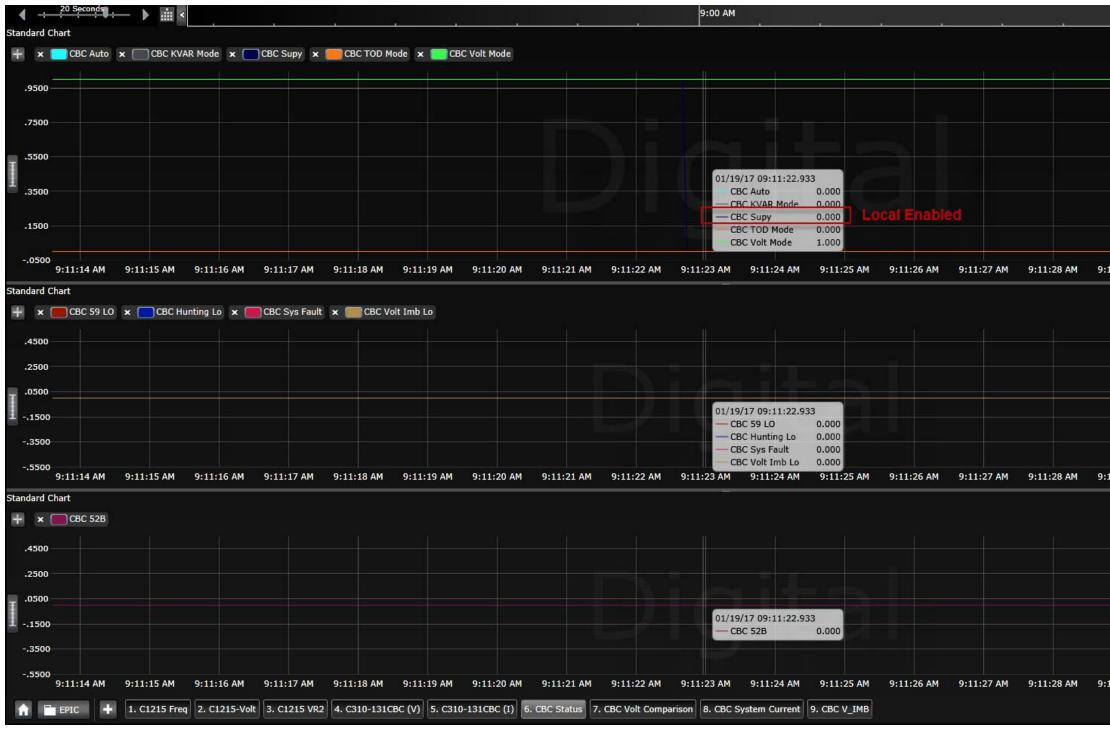

| Figure 7.9: CBC LOCAL Mode Enabled                                                                        | 125   |

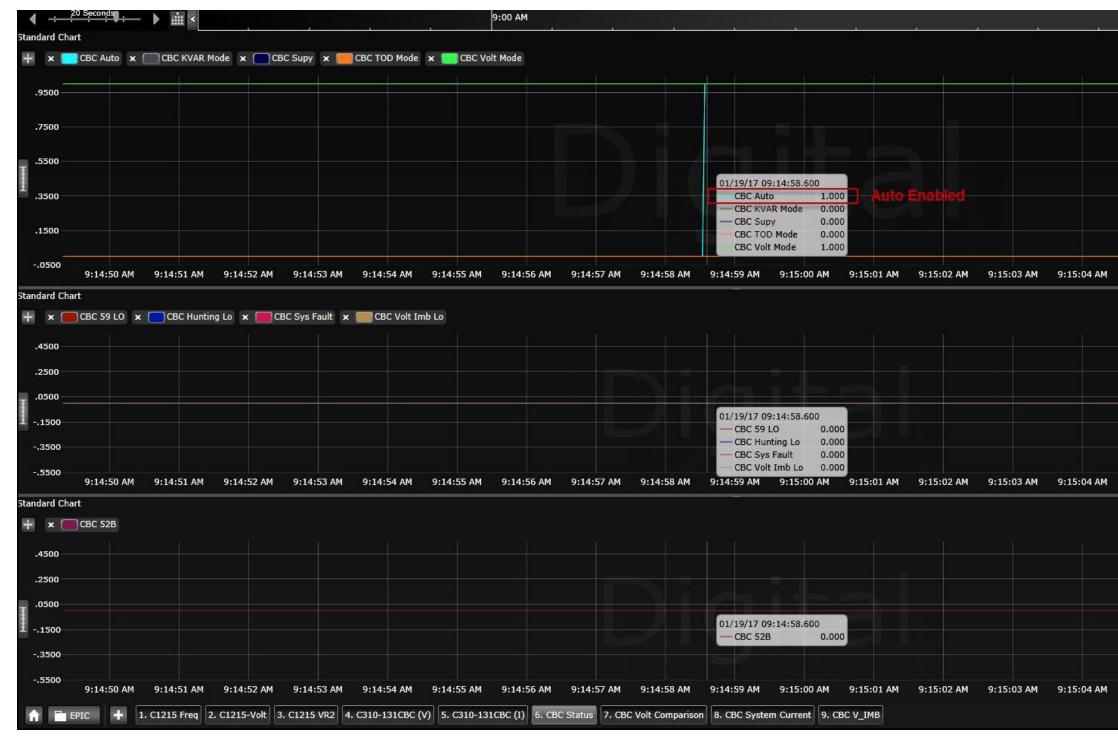

| Figure 7.10: CBC AUTO Mode Enabled                                                                        | 127   |

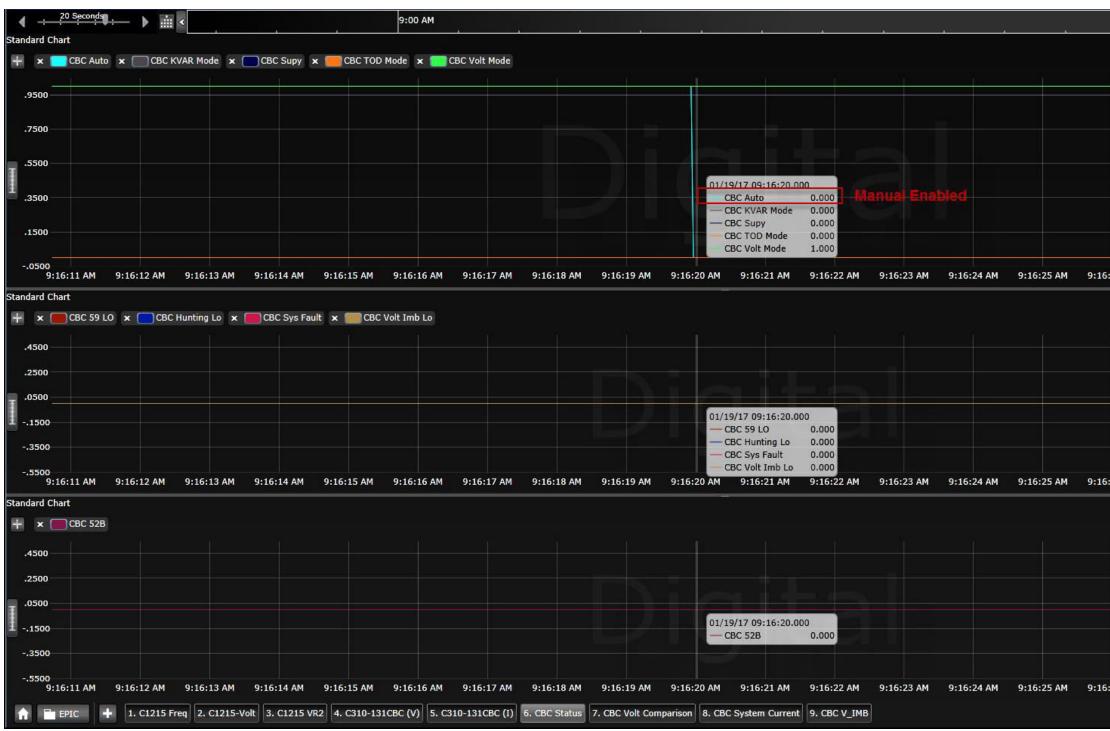

| Figure 7.11: CBC MANUAL Mode Enabled                                                                      | 128   |

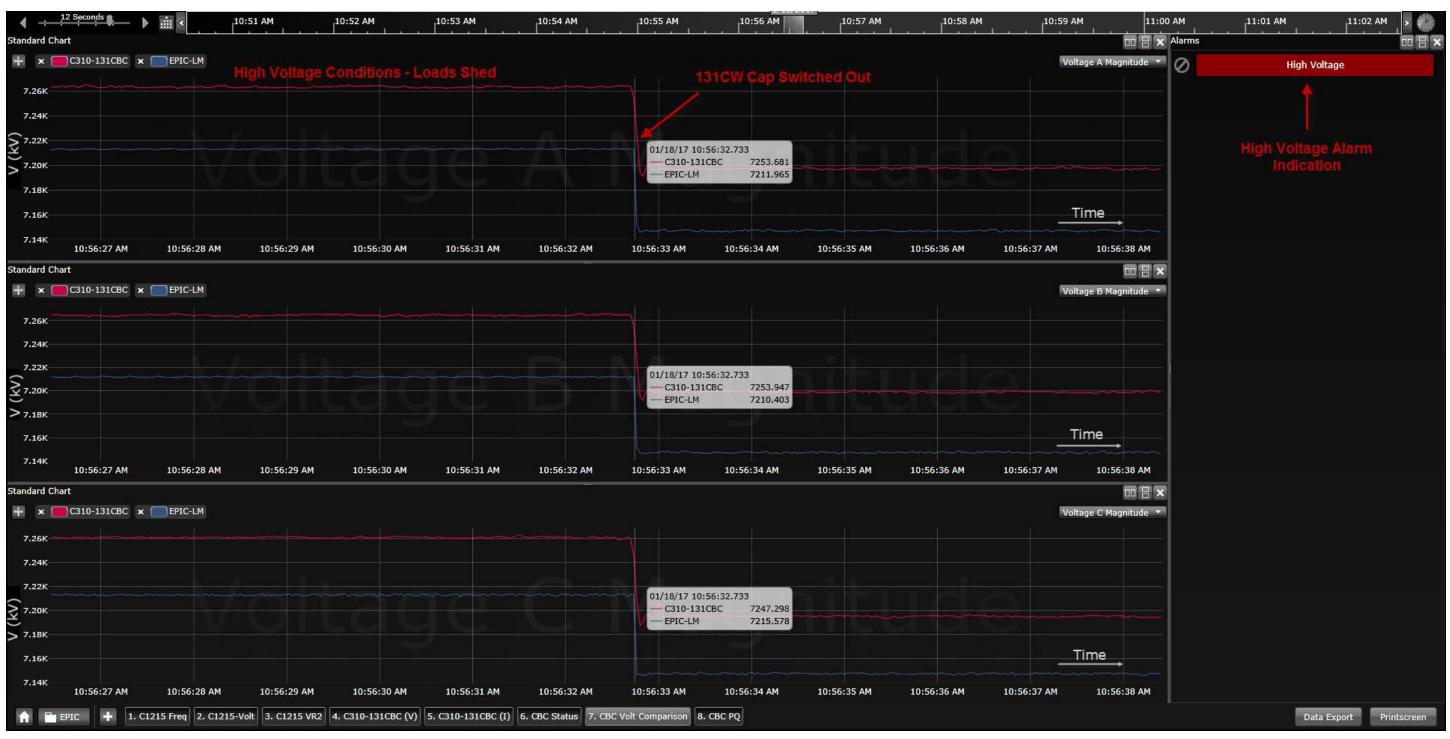

| Figure 7.12: CBC High-Voltage Condition                                                                   | 130   |

| Figure 7.13: CBC High-Voltage Switching Operation                                                         | 131   |

| Figure 7.14: CBC Low-Voltage Condition                                                                    | 133   |

| Figure 7.15: CBC Low-Voltage Switching Operation                                          | 134 |

|-------------------------------------------------------------------------------------------|-----|

| Figure 7.16: CBC Lead KVAR Condition – PQ Plot                                            | 136 |

| Figure 7.17: CBC Lead KVAR Condition – Voltage Plot                                       | 137 |

| Figure 7.18: CBC Lead KVAR Switching Operation                                            | 138 |

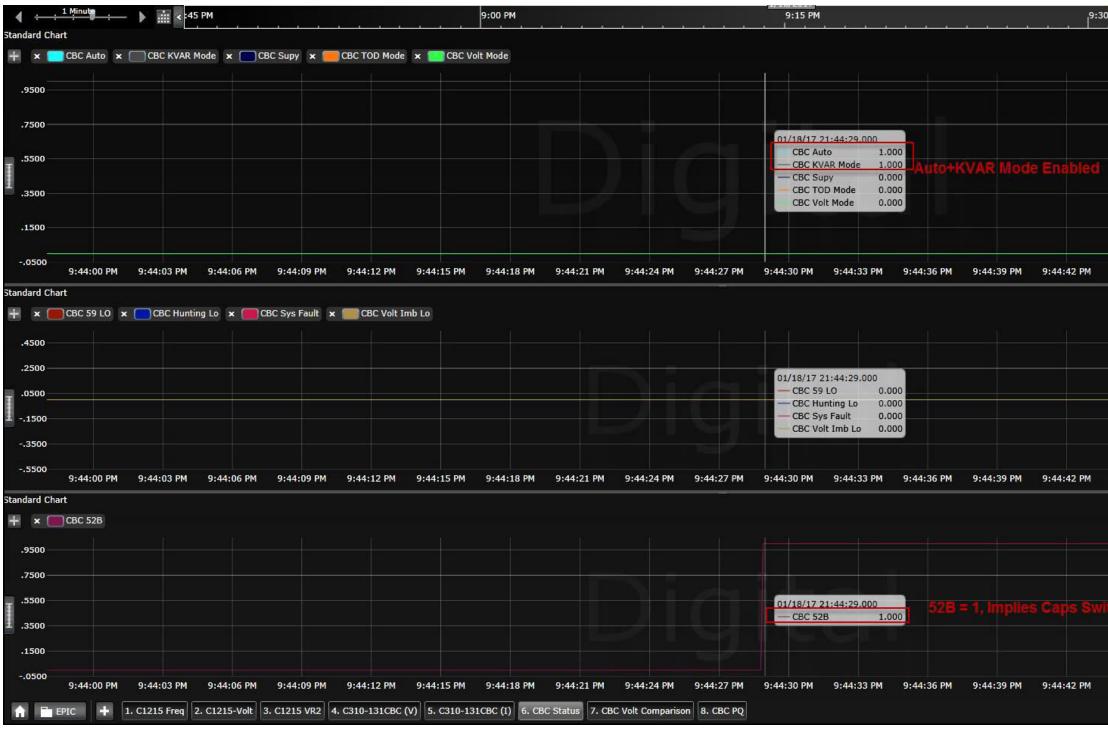

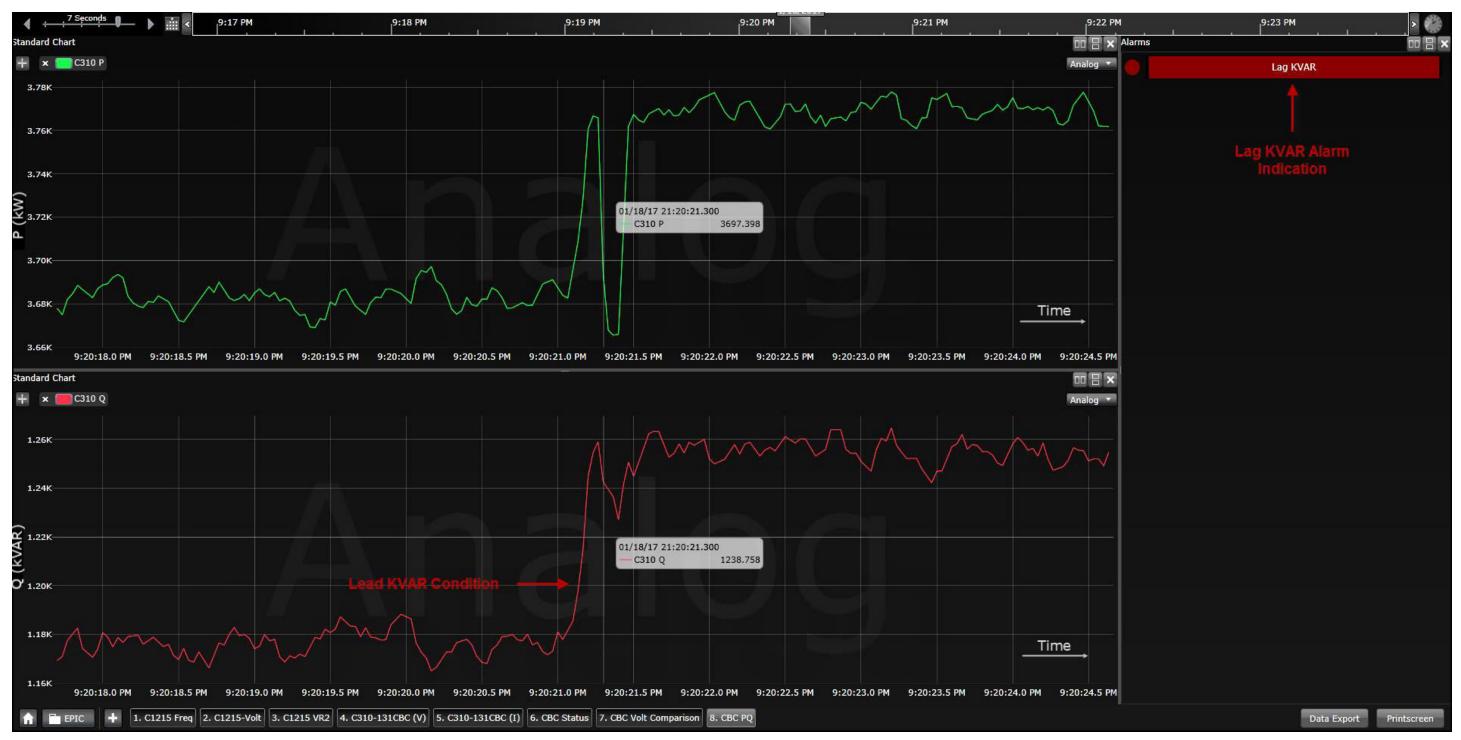

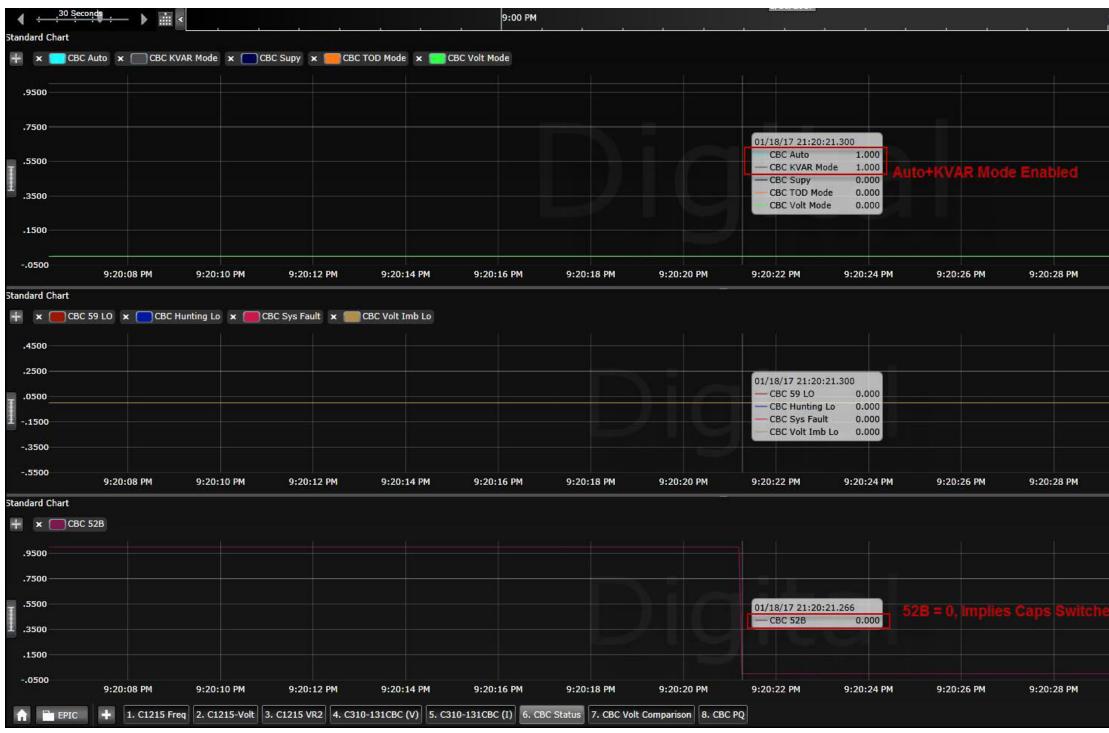

| Figure 7.19: CBC Lag KVAR Condition – PQ Plot                                             | 140 |

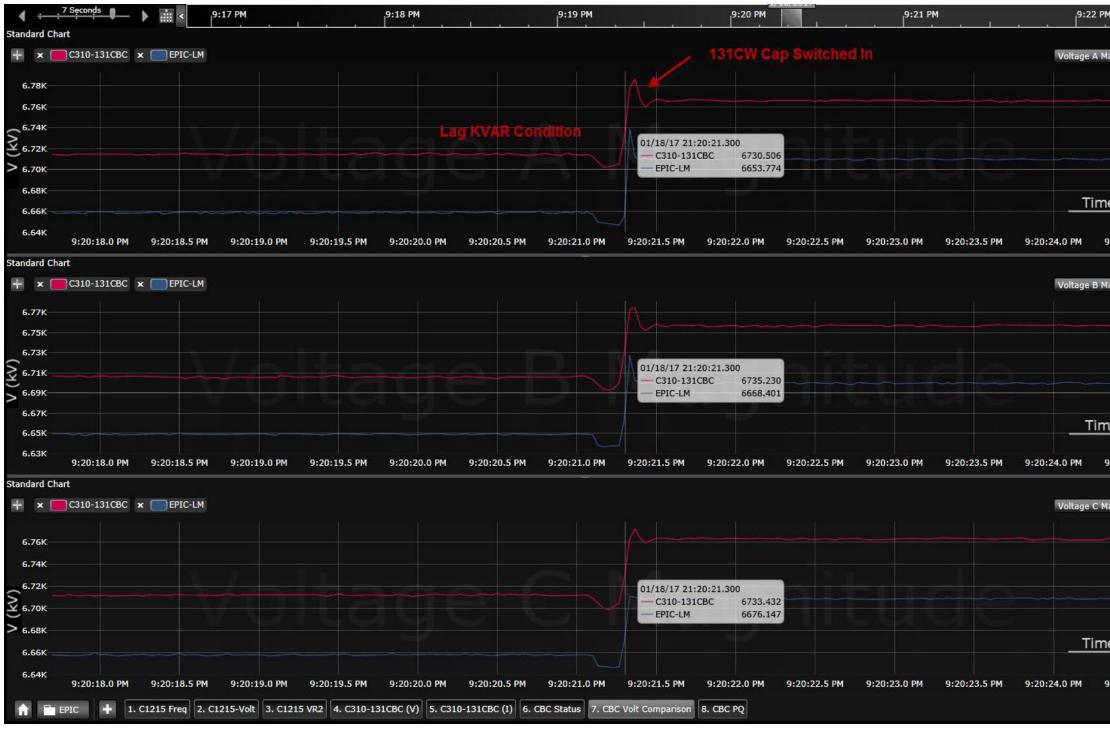

| Figure 7.20: CBC Lag KVAR Condition – Voltage Plot                                        | 141 |

| Figure 7.21: CBC Lag KVAR Switching Operation                                             | 142 |

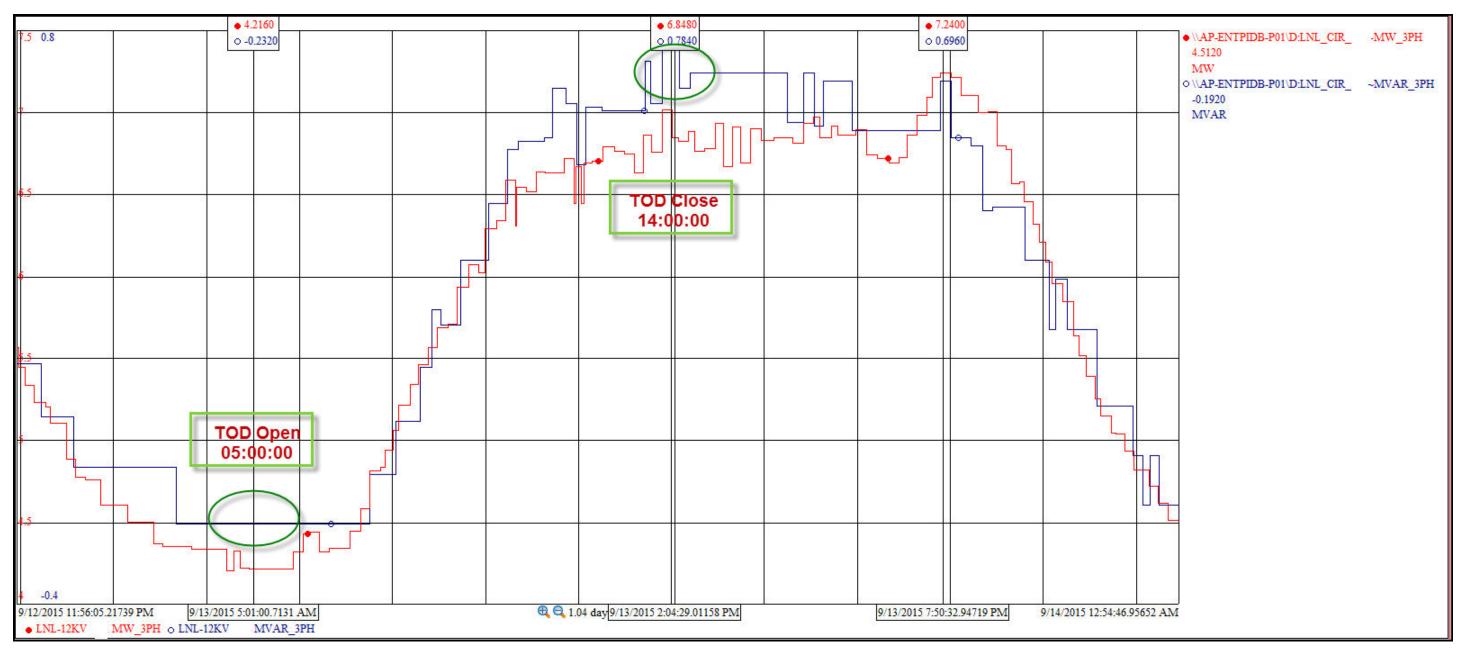

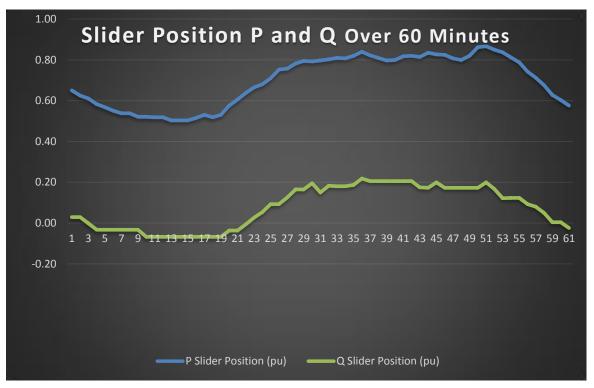

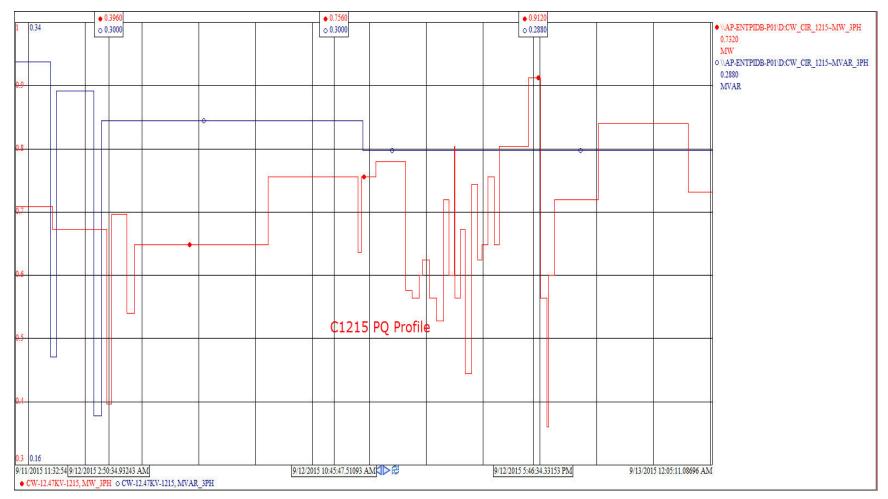

| Figure 7.22: Circuit PQ Profile Over 24 Hours                                             | 144 |

| Figure 7.23: CBC TOD Close Switching Operation at 14:00:00 Hours                          | 145 |

| Figure 7.24: CBC TOD Open Switching Operation at 05:00:00 Hours                           | 147 |

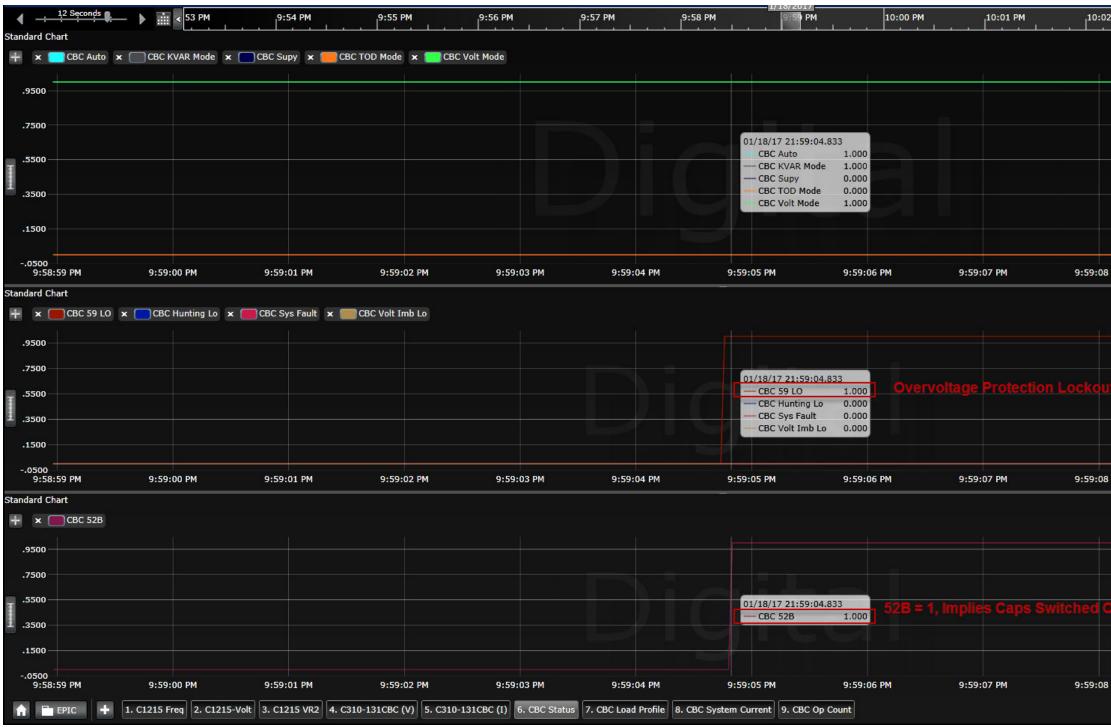

| Figure 7.25: CBC Overvoltage Condition                                                    | 149 |

| Figure 7.26: CBC Overvoltage Condition Lockout Operation                                  | 150 |

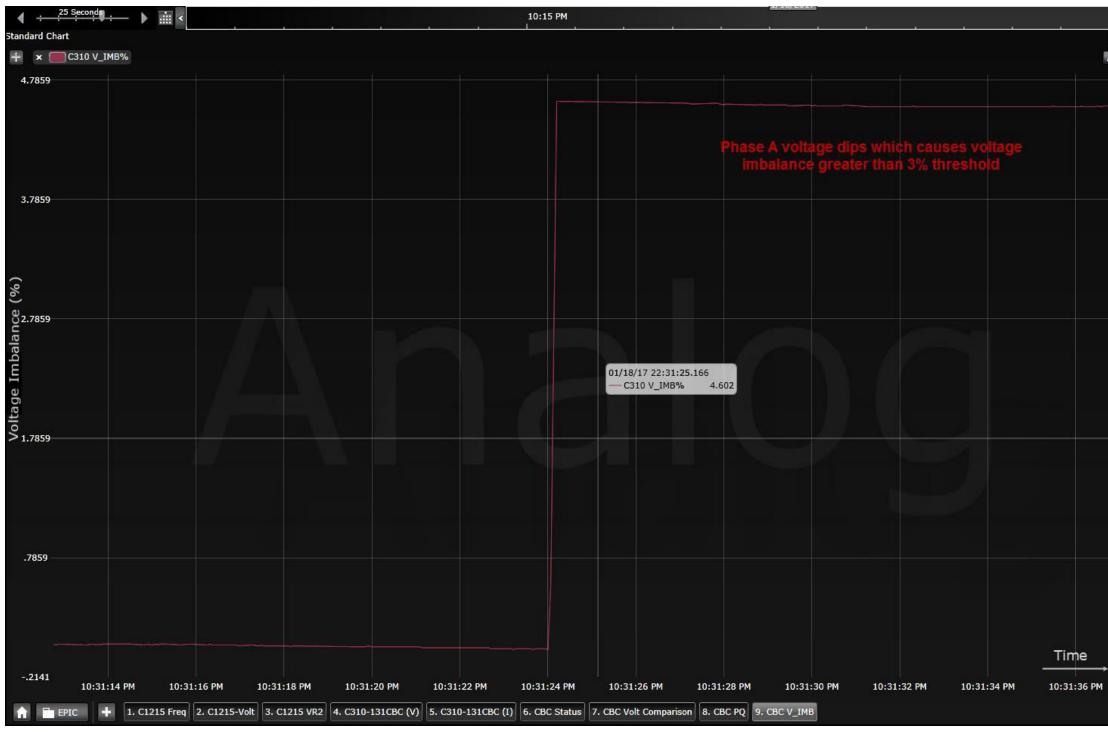

| Figure 7.27: CBC Voltage Imbalance Condition                                              | 152 |

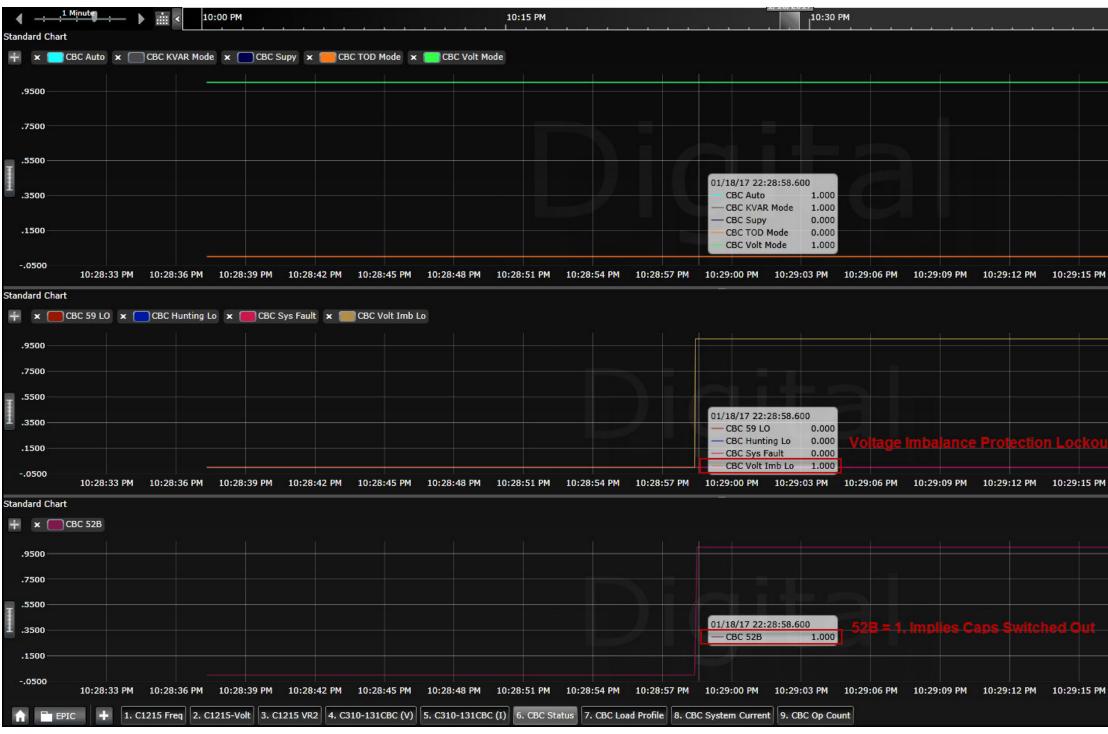

| Figure 7.28: CBC Voltage Imbalance Percentage                                             | 153 |

| Figure 7.29: CBC Voltage Imbalance Lockout Operation                                      | 154 |

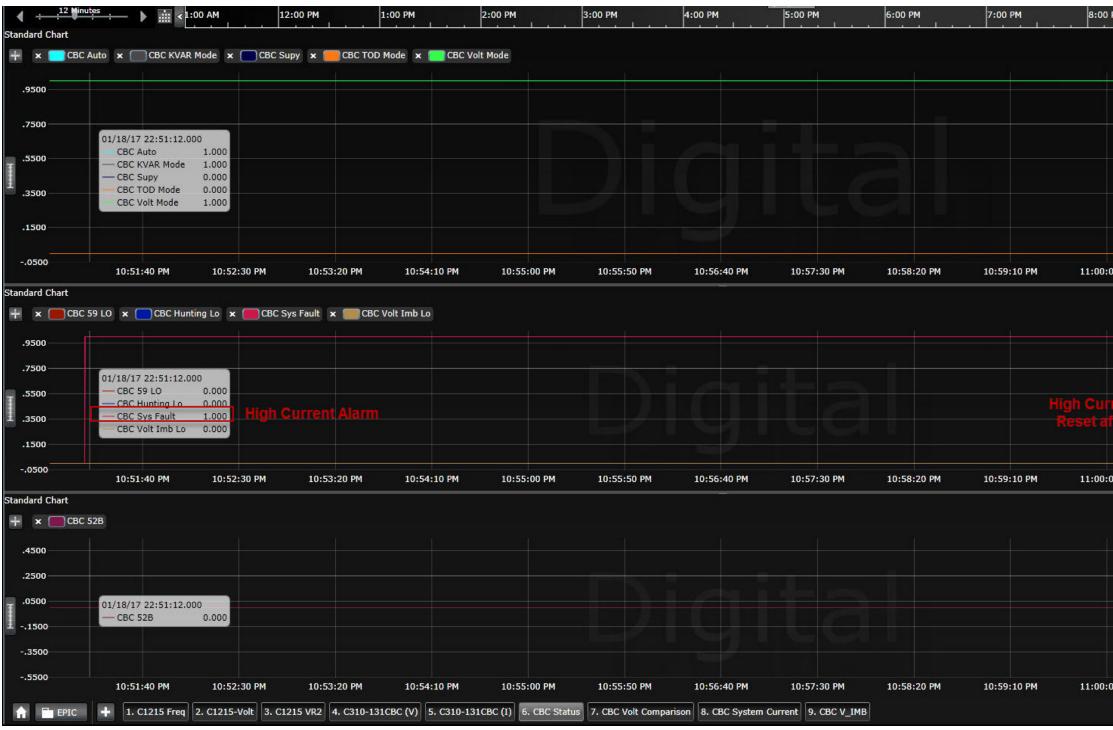

| Figure 7.30: CBC High-Current Condition                                                   | 156 |

| Figure 7.31: CBC High-Current Alarm Indication and Automatic Reset                        | 157 |

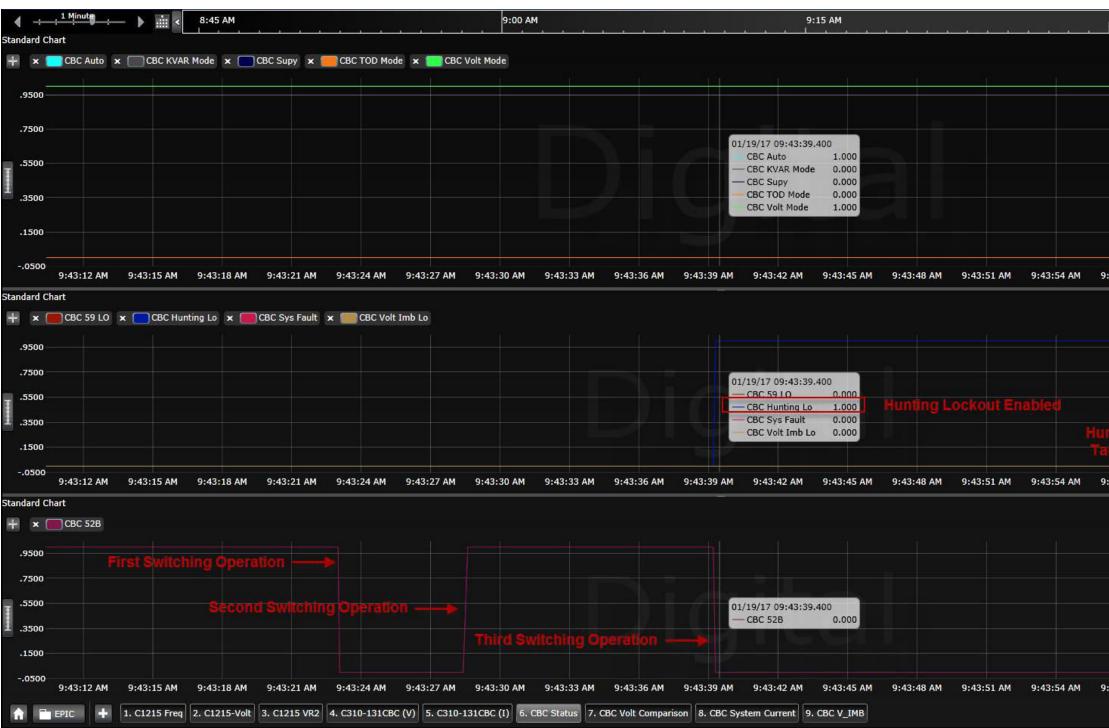

| Figure 7.32: CBC Hunting Lockout                                                          | 159 |

| Figure 7.33: CBC Operations Counter                                                       | 161 |

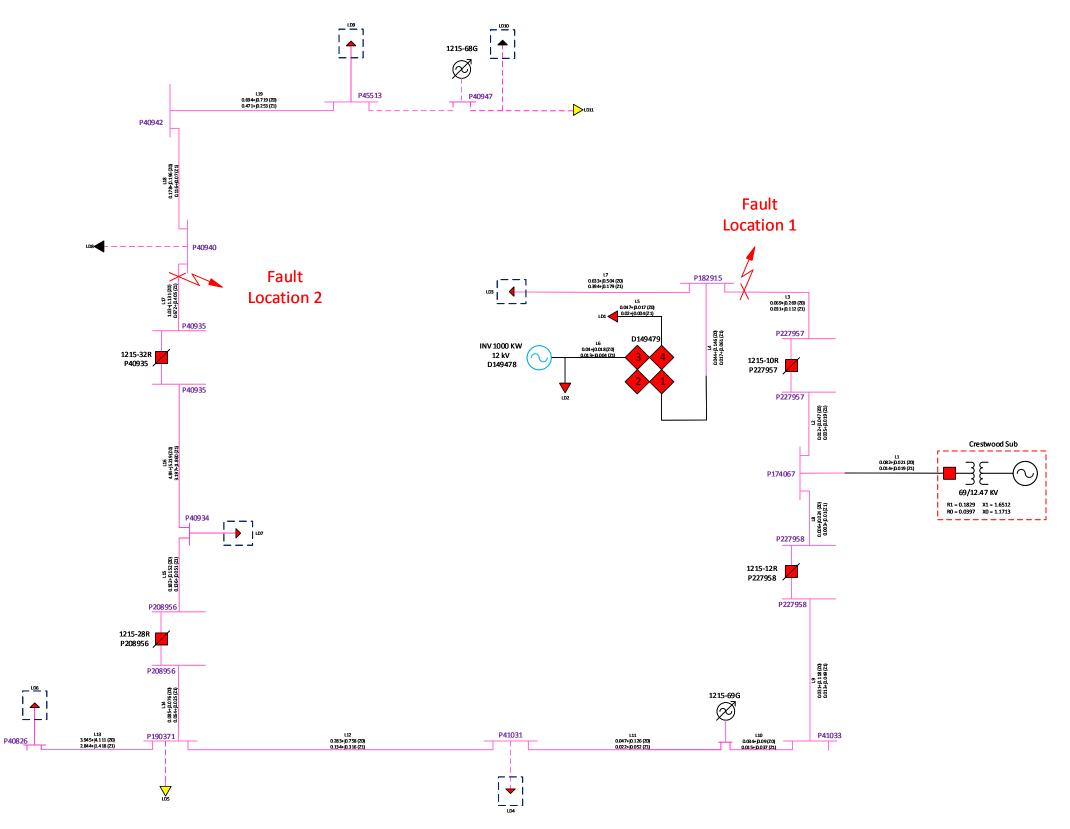

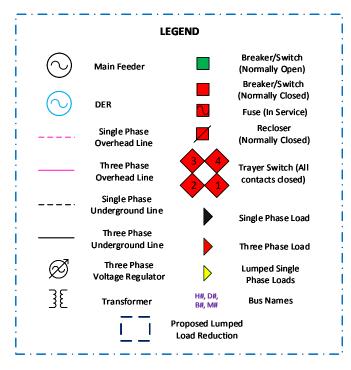

| Figure 8.1: Simplified One-Line Diagram With Fault Locations                              | 163 |

| Figure 8.2: HIF Detection Test Setup                                                      | 164 |

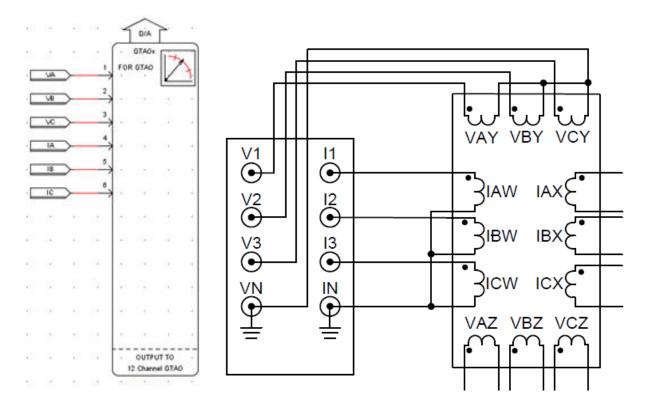

| Figure 8.3: Recloser RTDS Analog Output Signals                                           | 165 |

| Figure 8.4: Recloser Trip and Close Digital Input Wiring                                  | 167 |

| Figure 8.5: Block Diagram of HIF Detection in Recloser Control                            | 168 |

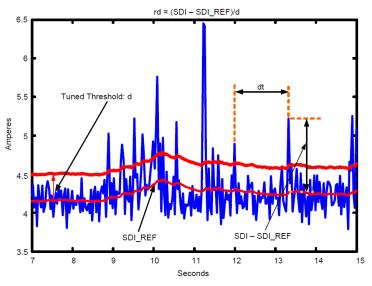

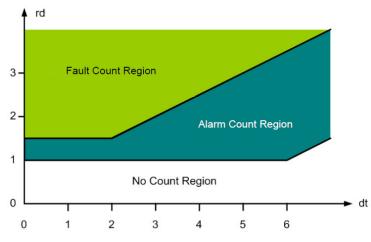

| Figure 8.6: HIF2 Algorithm Counting Parameters                                            | 169 |

| Figure 8.7: HIF2 Algorithm Counting Regions                                               | 169 |

| Figure 8.8: Test Setup                                                                    | 171 |

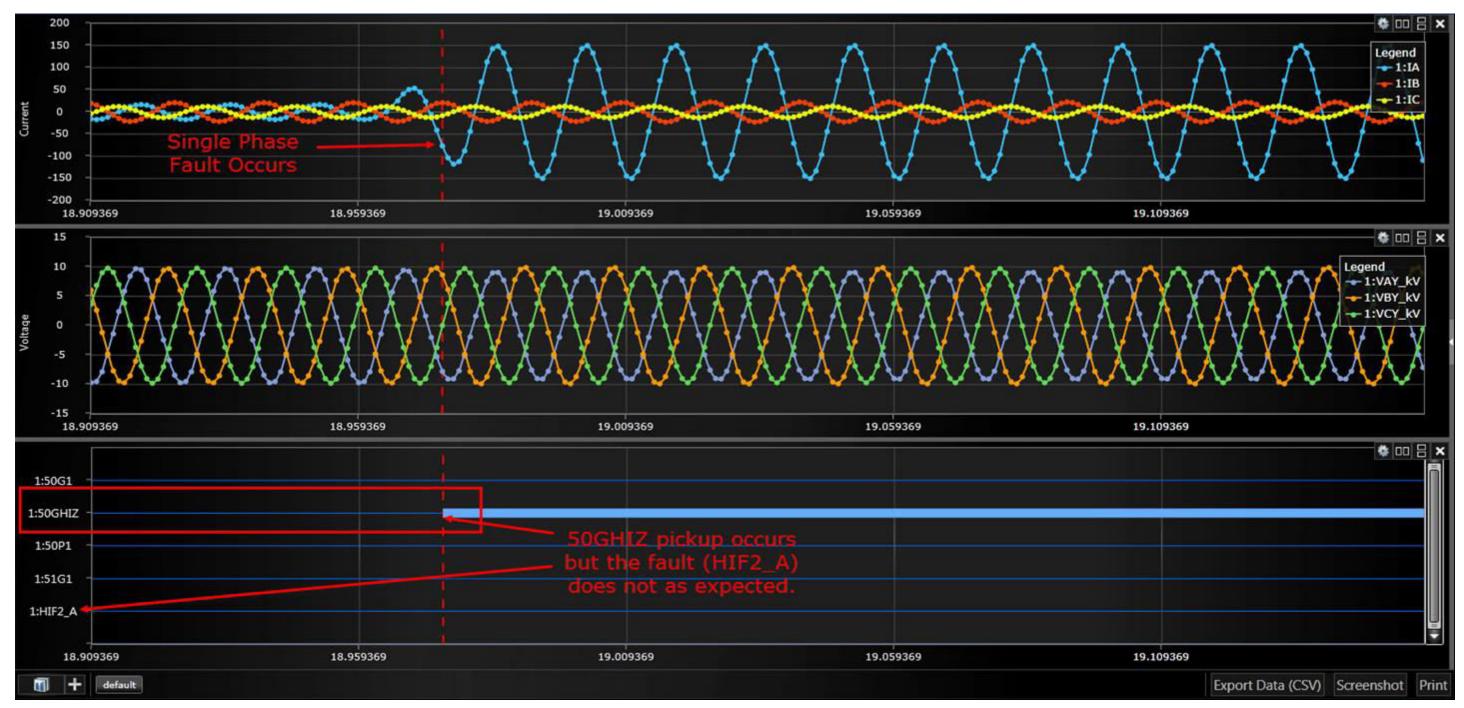

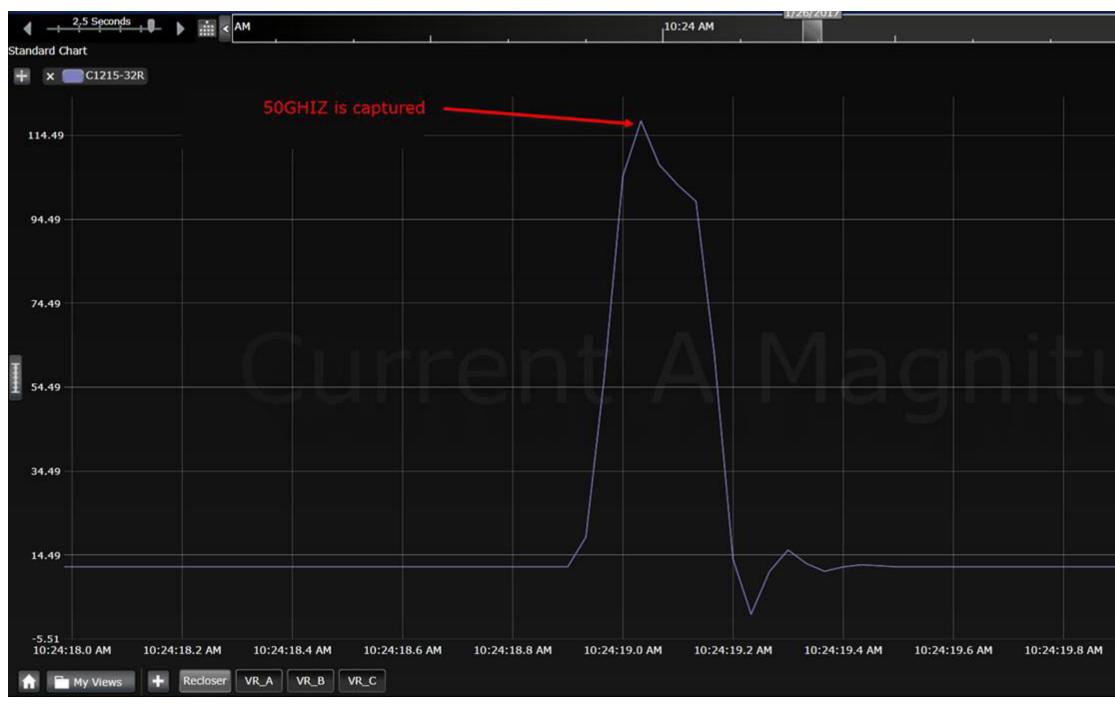

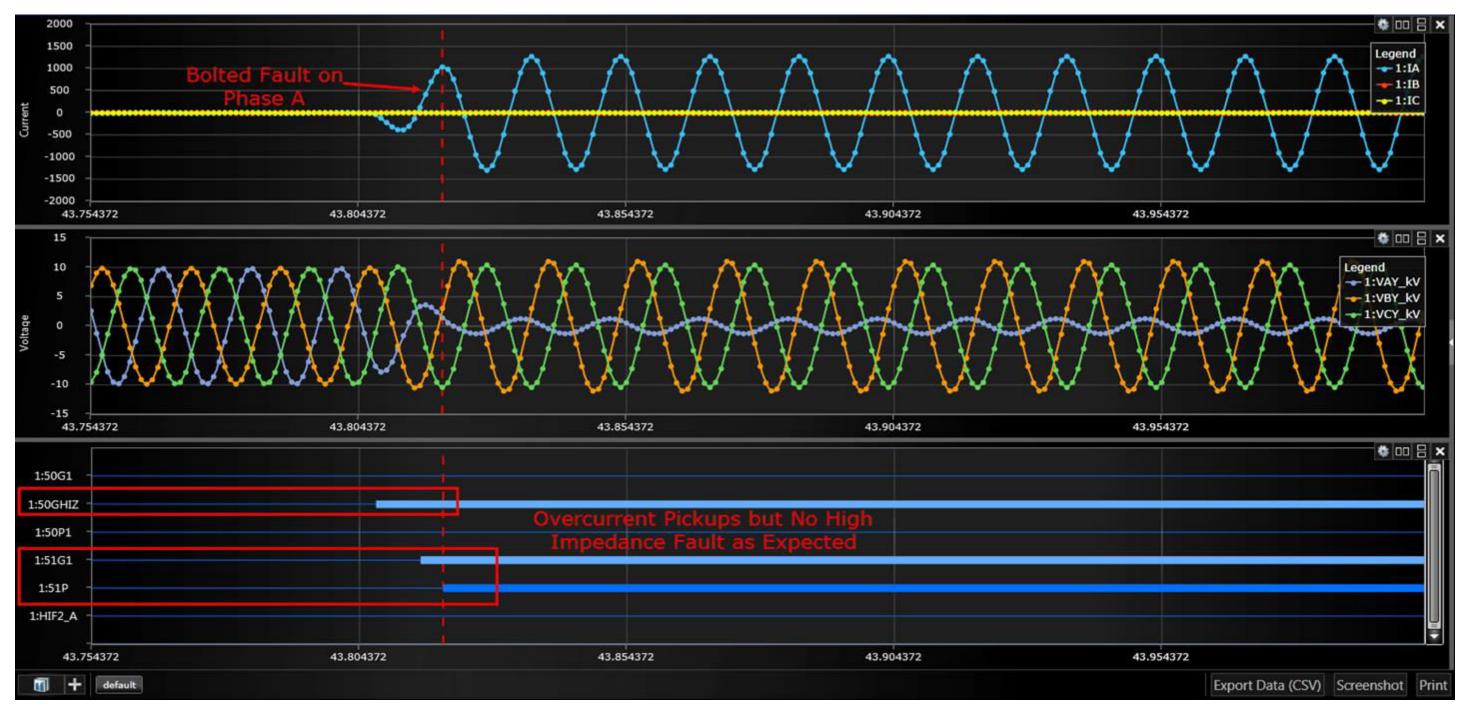

| Figure 8.9: Scenario 1 – Event Report – 50GHIZ Pickup                                     | 176 |

| Figure 8.10: Scenario 1 – C1215-32R Current A Magnitude – Single Spike                    | 177 |

| Figure 8.11: Scenario 1 – SER Report – 50GHIZ Pickup                                      | 178 |

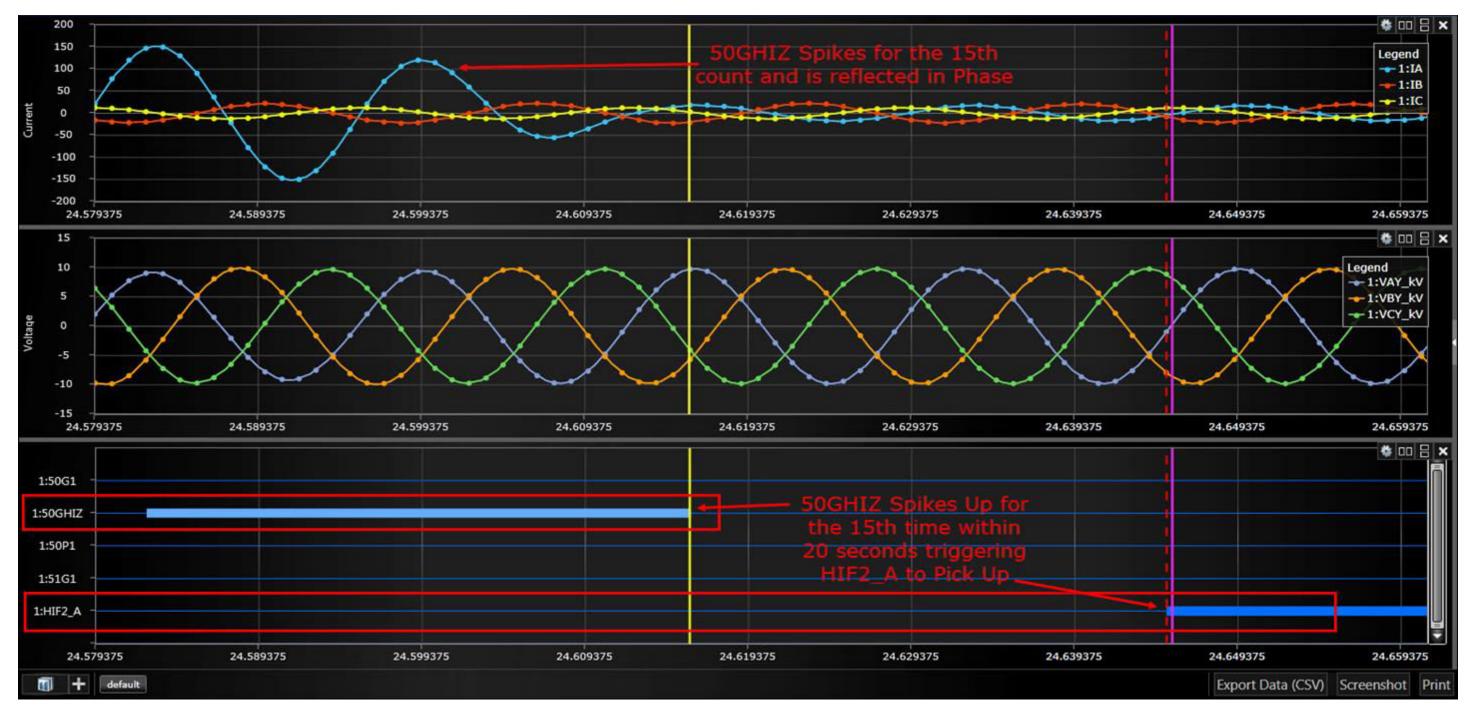

| Figure 8.12: Scenario 2 – Event Report – 50GHIZ and HIF2_A Pickup                         | 180 |

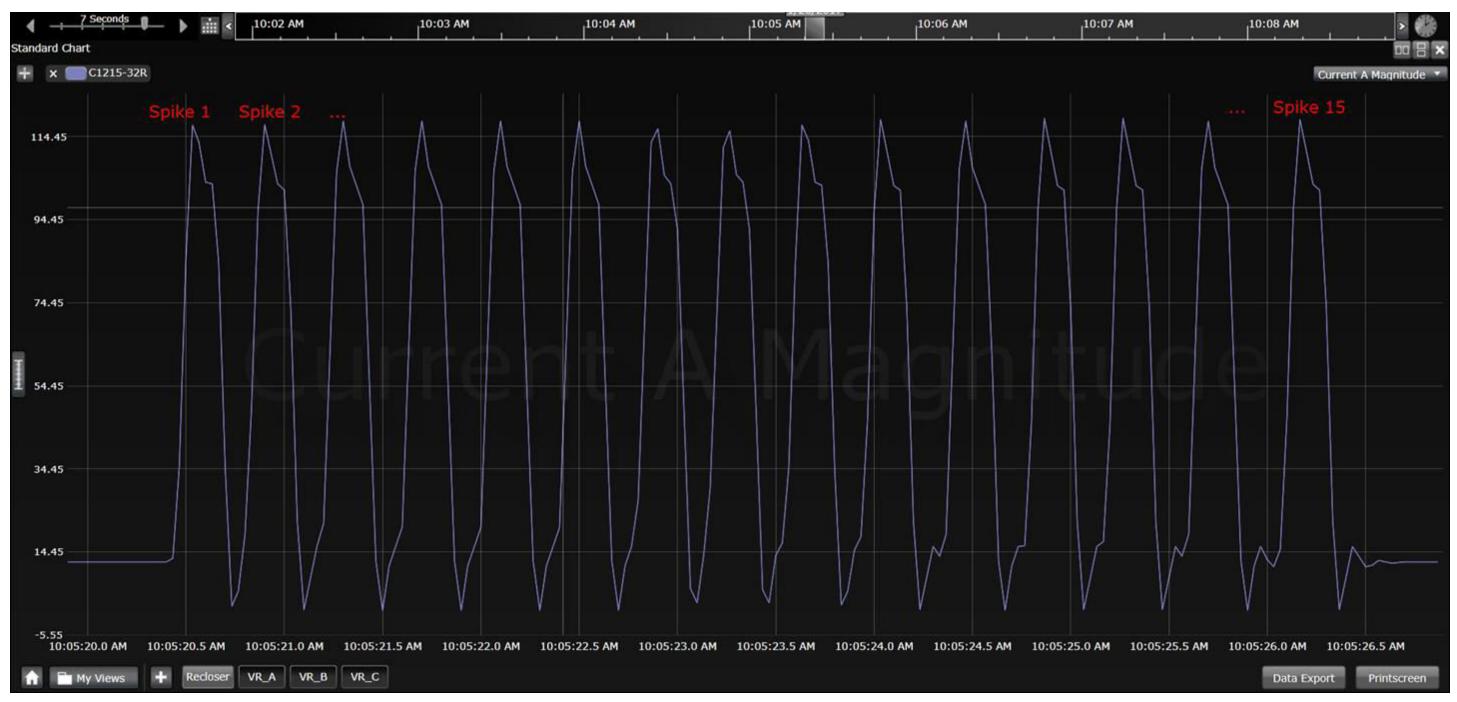

| Figure 8.13: Scenario 2 – Central C1215-32R Pickup                                        | 181 |

| Figure 8.14: Scenario 2 – SER Report – 50GHIZ Picks Up 15 Times to Trigger HIF2_A         |     |

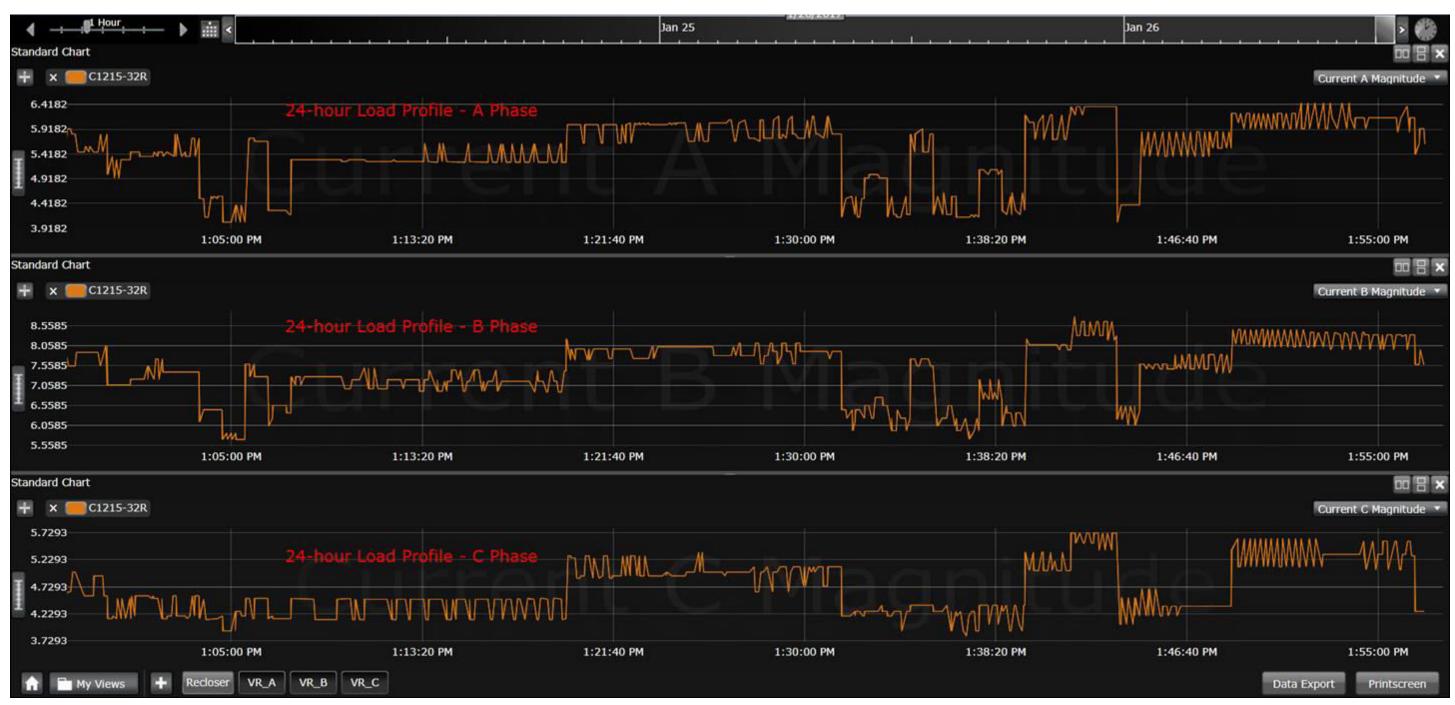

| Figure 8.15: Scenario 3 – Central with 24-Hour Load Profile                               | 184 |

| Figure 8.16: Scenario 3 – SER Shows No Pickup on a 24-Hour Load Profile Cycle as Expected |     |

| Figure 8.17: Scenario 4 – Overcurrent Protection Pickups with No HIF Pickup               | 187 |

| Figure 8.18: Scenario 4 – Central Single Spike Does Not Meet HIF Criteria                 | 188 |

| Figure 8.19: Scenario 4 – SER Shows Expected Overcurrent Pickups                   |     |

|------------------------------------------------------------------------------------|-----|

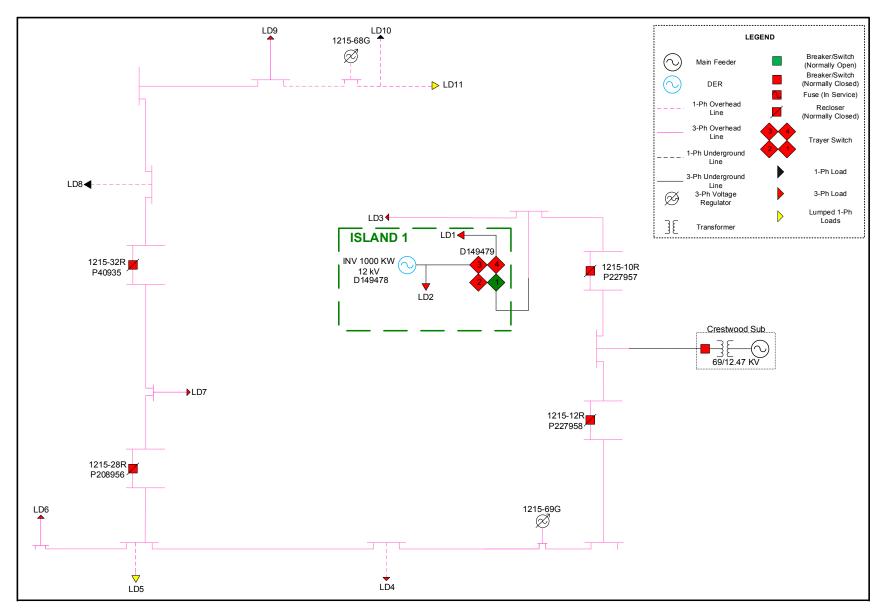

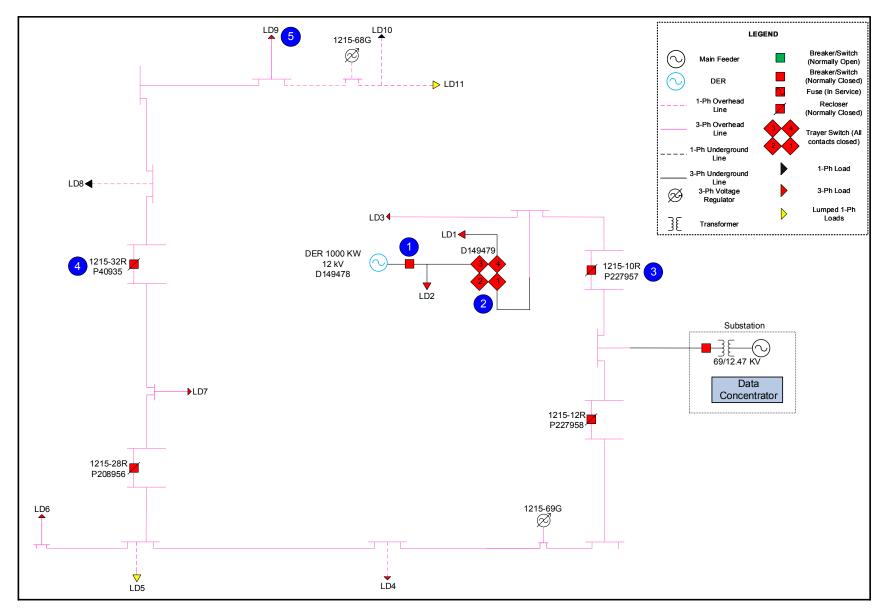

| Figure 9.1: Desert-Rural Test Circuit – Island 1                                   |     |

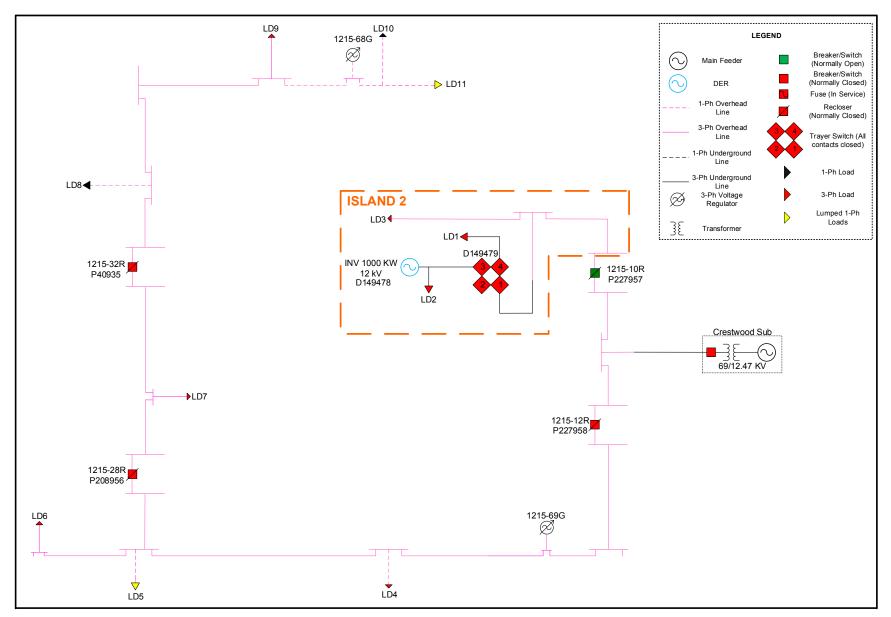

| Figure 9.2: Desert-Rural Test Circuit – Island 2                                   |     |

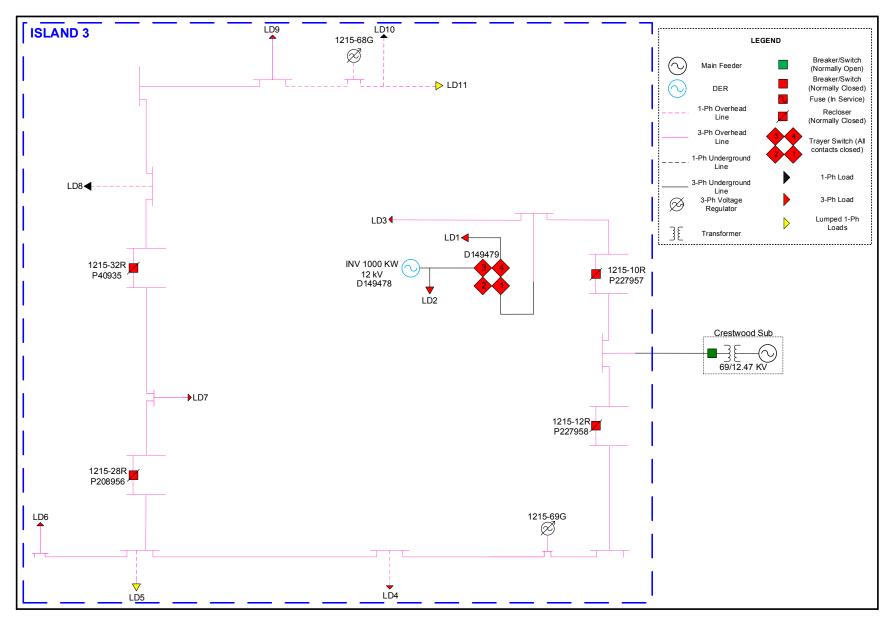

| Figure 9.3: Desert-Rural Test Circuit – Island 3                                   |     |

| Figure 9.4: Locations of PMUs                                                      |     |

| Figure 9.5: RTDS and PMUs Interface                                                |     |

| Figure 9.6: Synchrophasor Communications Architecture                              |     |

| Figure 9.7: Voltage Monitoring in Island 3                                         |     |

| Figure 9.8: Frequency Monitoring in Island 3                                       |     |

| Figure 10.1: Desert-Rural Test Circuit                                             |     |

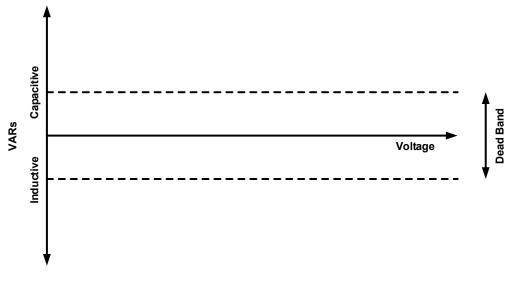

| Figure 10.2: Volt/VAR Mode Operation                                               |     |

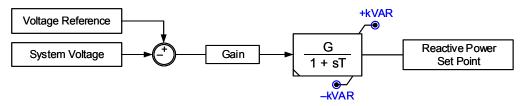

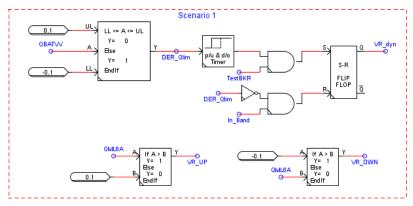

| Figure 10.3: Volt/VAR Controller Logic                                             |     |

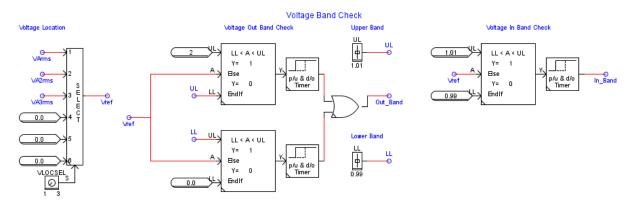

| Figure 10.4: Voltage Band Check                                                    |     |

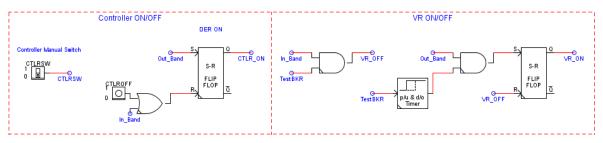

| Figure 10.5: Controller On/Off Logic                                               |     |

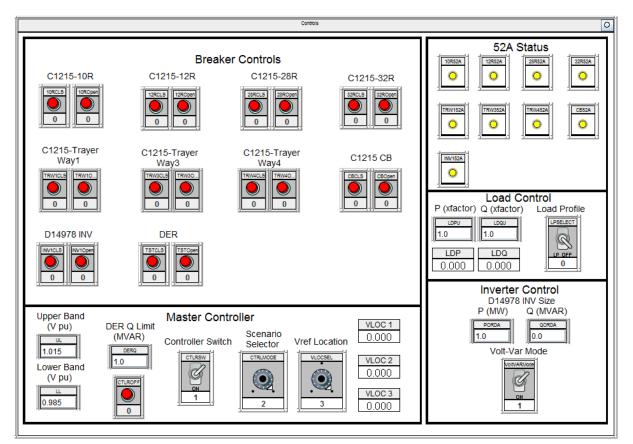

| Figure 10.6: Voltage Control – Scenario 1                                          |     |

| Figure 10.7: Voltage Control – Scenario 2                                          |     |

| Figure 10.8: DER Test RunTime Controls                                             |     |

| Figure 10.9: Voltage Support Coordination Scenario Operation                       |     |

| Figure 10.10: Scenario 1 RunTime Plot                                              |     |

| Figure 10.11: Scenario 2 RunTime Plot                                              | 217 |

| Figure 11.1: Voltage Profile With Voltage Regulator In Service                     |     |

| Figure 12.1: Data Flow for Advanced Control of System Voltage Coordination         |     |

| Figure 12.2: Energized Downed Conductor Causes Arcing – Potential Safety Hazard    |     |

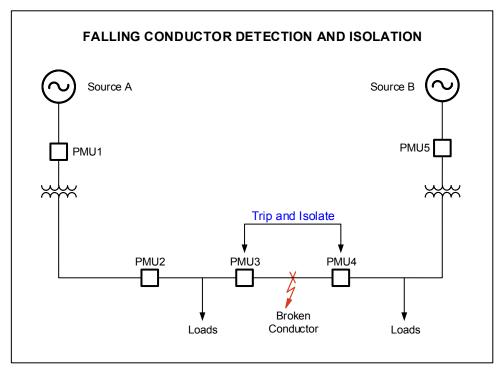

| Figure 12.3: Falling Conductor Detection and Isolation                             |     |

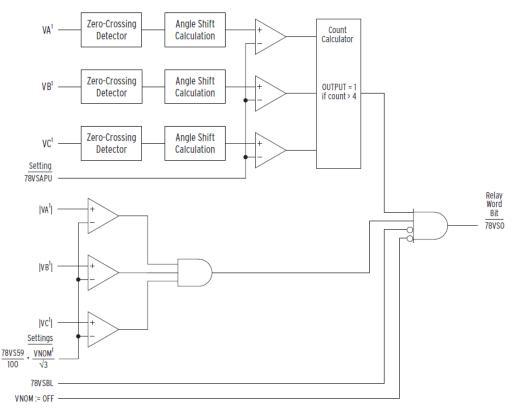

| Figure 12.4: Vector Shift Element Logic                                            |     |

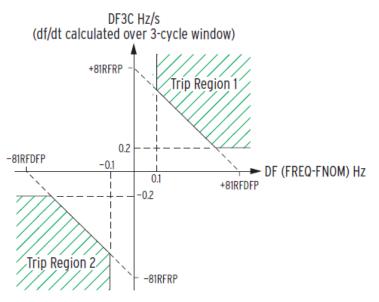

| Figure 12.5: 81RF Characteristics                                                  |     |

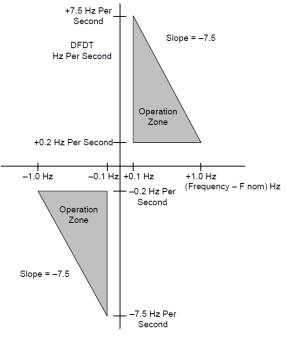

| Figure 12.6: Fast df/dt Logic                                                      |     |

| Figure 12.7: Power Quality Data Collection and Analysis                            |     |

| Figure A.1: Coastal-Residential Test Circuit One-Line Diagram                      |     |

| Figure A.2: Urban Test Circuit One-Line Diagram                                    |     |

| Figure A.3: Desert-Rural Test Circuit One-Line Diagram                             |     |

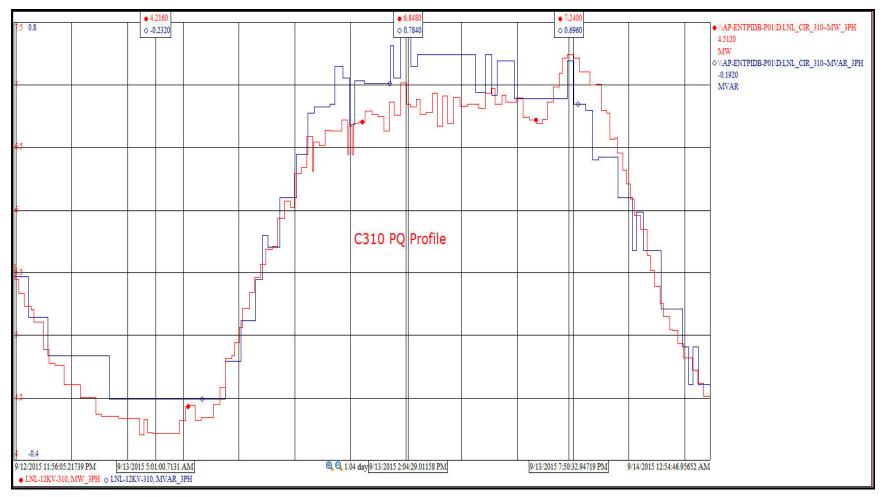

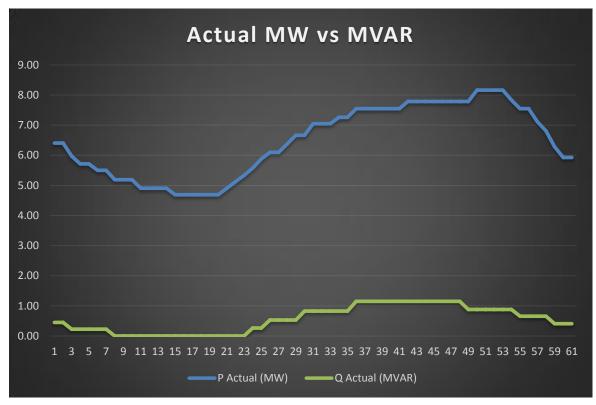

| Figure B.1: Coastal-Residential Test Circuit – Actual Load Profile Over 24 Hours   |     |

| Figure B.2: Coastal-Residential Test Circuit – Actual Load Profile Over 60 Minutes |     |

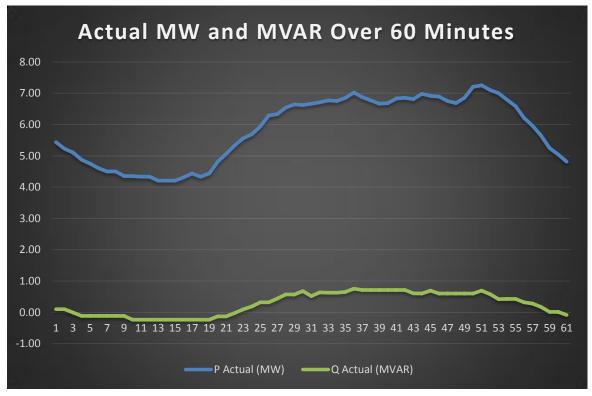

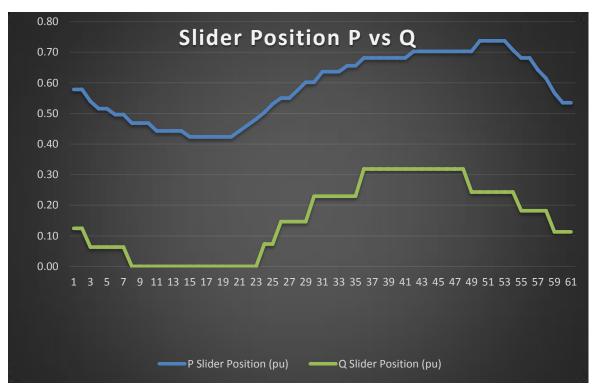

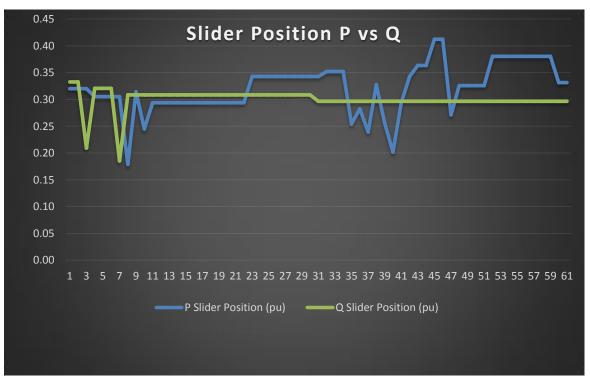

| Figure B.3: Coastal-Residential Test Circuit – Slider Position Over 60 Minutes     |     |

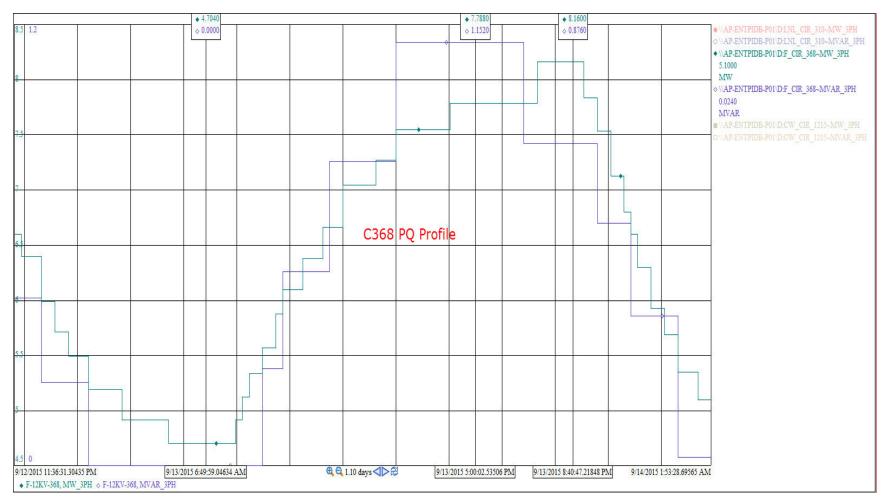

| Figure B.4: Urban Test Circuit – Actual Load Profile Over 24 Hours                 | 245 |

| Figure B.5: Urban Test Circuit – Actual Load Profile Over 60 Minutes               |     |

| Figure B.6: Urban Test Circuit – Slider Position Over 60 Minutes                   |     |

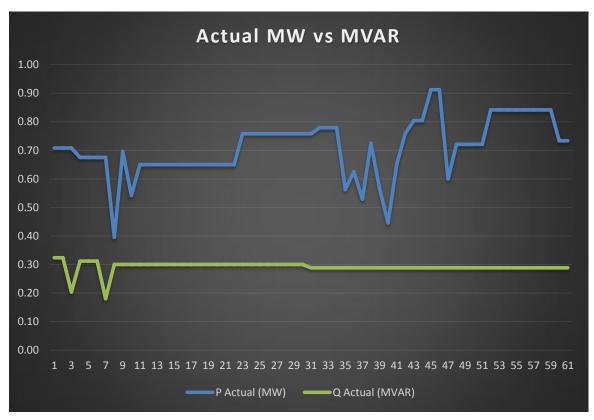

| Figure B.7: Desert-Rural Test Circuit – Actual Load Profile Over 24 Hours   | 249 |

|-----------------------------------------------------------------------------|-----|

| Figure B.8: Desert-Rural Test Circuit – Actual Load Profile Over 60 Minutes | 250 |

| Figure B.9: Desert-Rural Test Circuit – Slider Position Over 60 Minutes     | 250 |

## List of Tables

| Table 3.1: Technical Specifications of the D-VAR System                     |    |

|-----------------------------------------------------------------------------|----|

| Table 3.2: ANSI/IEEE C57.104 Standard for Dissolved Gas Analyses            |    |

| Table 3.3: Comparison of Vendor I and Vendor B FRA Devices                  |    |

| Table 3.4: Transformer Monitor Analog and Digital I/O Monitoring Parameters |    |

| Table 3.5: SAE J1772TM-2011 Charging Configurations and Rating Terminology  |    |

| Table 3.6: Vendor E EVSE Networking Specification                           |    |

| Table 6.1: Voltage Regulator Operation and Indication LED Definitions       |    |

| Table 6.2: Voltage Regulator Operator-Controlled Pushbuttons                |    |

| Table 6.3: Voltage Regulator Control I/O List                               | 67 |

| Table 6.4: Auto and Remote Toggle – Local Control                           |    |

| Table 6.5: High-Voltage Lower Tap Operation                                 |    |

| Table 6.6: Low-Voltage Raise Tap Operation                                  |    |

| Table 6.7: Voltage High- and Low-Limit Operations                           |    |

| Table 6.8: Load Profile Operation                                           |    |

| Table 7.1: Controller I/O List                                              |    |

| Table 7.2: Capacitor Bank Controller Analog Thresholds                      |    |

| Table 7.3: SUPY and LOCAL Toggle                                            |    |

| Table 7.4: AUTO and MANUAL Toggle – LOCAL Control                           |    |

| Table 7.5: High-Voltage Open Operation                                      |    |

| Table 7.6: Low-Voltage Close Operation                                      |    |

| Table 7.7: Leading KVAR Open Operation (+P)                                 |    |

| Table 7.8: Lagging KVAR Close Operation (+P)                                |    |

| Table 7.9: TOD Close Operation                                              |    |

| Table 7.10: TOD Open Operation                                              |    |

| Table 7.11: Overvoltage Lockout                                             |    |

| Table 7.12: Voltage Imbalance Lockout                                       |    |

| Table 7.13: High-Current Condition                                          |    |

| Table 7.14: Hunting Lockout                                                 |    |

| Table 8.1: HIF Relay Word Bits                                              |    |

| Table 8.2: Recloser Control I/O List                                        |    |

| Table 8.3: Auto and Remote Toggle – Local Control                           |    |

| Table 8.4: 50GHIZ Overcurrent Pickup Element Test                           |    |

| Table 8.5: HIF Detection                                                    |    |

| Table 8.6: Recloser Response During Load Profile Operation       173                                                     |

|--------------------------------------------------------------------------------------------------------------------------|

| Table 8.7: Recloser Operation During Bolted Fault         176                                                            |

| Table 9.1: Desert-Rural Test Circuit – Load Distribution                                                                 |

| Table 9.2: ANSI C84.1-2006 Standard Nominal System Voltages and Voltages Range – Service Voltage                         |

| Table 9.3: ANSI C84.1-2006 Standard Nominal System Voltages and Voltages Range – Utilization         Voltage         188 |

| Table 9.4: IEEE 519-2014 Maximum Harmonic Current Distortion in Percent of Current                                       |

| Table 9.5: IEEE 519-2014 Maximum Harmonic Voltage Distortion in Percent       190                                        |

| Table 10.1: Load Switching                                                                                               |

| Table 11.1: Desert-Rural Test Circuit Voltage Levels                                                                     |

| Table 15.1: EPIC Primary and Secondary Guiding Principles         224                                                    |

| Table B.1: Load and Slider Position Value – Coastal-Residential Test Circuit                                             |

| Table B.2: Load and Slider Position Value – Urban Test Circuit                                                           |

| Table B.3: Load and Slider Position Value – Desert-Rural Test Circuit       243                                          |

# **Abbreviations and Acronyms**

| ACSI  | abstract communication service interface  | HVRT   | high-voltage ride-through                            |

|-------|-------------------------------------------|--------|------------------------------------------------------|

| ADC   | analog-to-digital converter               | ICE    | internal combustion engine                           |

| ANSI  | American national Standards Institute     | IEC    | International Electrotechnical Commission            |

| AR    | automatic reconfiguration                 | IED    | intelligent electronic device                        |

| AVR   | automatic voltage regulator               | IEEE   | Institute of Electrical and Electronics              |

| BCD   | binary-coded decimal                      |        | Engineers                                            |

| BEV   | battery electric vehicle                  | IFRA   | impulse frequency response analysis                  |

| CBC   | capacitor bank controller                 | IGBT   | insulated-gate bipolar transistor                    |

| CES   | Community Energy Storage                  | IIR    | infinite impulse response                            |

| СТ    | current transformer                       | I/O    | input/output                                         |

| CVR   | conservation voltage reduction            | IP     | Internet Protocol                                    |

| DA    | Distribution Automation                   | IRIG-B | Inter-Range Instrumentation Group time code format B |

| DAC   | Distribution Automation Controller        | ISM    | industrial, scientific, and medical                  |

| ADAC  | Advanced Distribution Automation Control  | ISO    | International Organization for                       |

| DCLS  | dc level shift                            |        | Standardization                                      |

| DER   | distributed energy resource               | KVAR   | kilovolt-ampere reactive                             |

| df/dt | rate-of-change-of-frequency               | LAN    | local-area network                                   |

| DFO   | dynamic feeder optimization               | LED    | light-emitting diode                                 |

| DG    | distributed generator                     | LTC    | load tap changer                                     |

| DGA   | dissolved gas analysis                    | LVRT   | low-voltage ride-through                             |

| DNP3  | Distributed Network Protocol              | MAC    | medium access control                                |

| DST   | daylight-saving time                      | ME     | multiended                                           |

| D-VAR | dynamic volt-ampere reactive              | MMS    | manufacturing message specification                  |

| DVR   | dynamic voltage regulator                 | NC     | normally closed                                      |

| EPIC  | Electric Program Investment Charge        | NEC    | National Electric Code                               |

| EV    | electric vehicle                          | NO     | normally open                                        |

| EVSE  | electrical vehicle supply equipment       | NTP    | Network Time Protocol                                |

| FFT   | fast Fourier transform                    | OCPP   | Open Charge Point Protocol                           |

| FRA   | frequency response analysis               | OF     | overfrequency                                        |

| FTP   | File Transfer Protocol                    | OLE    | object linking and embedding                         |

| GFCI  | ground-fault circuit interrupter          | OLTC   | on-load tap changer                                  |

| GOOSE | Generic Object-Oriented Substation Event  | OPC    | OLE for Process Control                              |

| GPS   | Global Positioning System                 | OSI    | Open System Interface                                |

| GSE   | generic substation event                  | OV     | overvoltage                                          |

| GSSE  | generic substation status event           | Р      | active power                                         |

| GTAO  | gigabit transceiver analog output         | PCC    | point of common coupling                             |

| GTFPI | gigabit transceiver front-panel interface | PCS    | Power Conversion System                              |

| HIF   | high-impedance fault                      | PDC    | phasor data concentrator                             |

| HIL   | hardware-in-the-loop                      | PHEV   | plug-in hybrid electric vehicle                      |

|       |                                           |        | ro majora ciccare venere                             |

| PHY   | physical layer                                |

|-------|-----------------------------------------------|

| PID   | proportional integral derivative              |

| PLC   | programmable logic controller                 |

| PMU   | phasor measurement unit                       |

| ppm   | parts per million                             |

| PT    | potential transformer                         |

| PTP   | Precision Time Protocol                       |

| pu    | per unit                                      |

| PV    | photovoltaic                                  |

| Q     | reactive power                                |

| rms   | root-mean-square                              |

| RSCAD | RTDS Power Simulation Software                |

| RTAC  | Real-Time Automation Controller               |

| RTD   | resistance temperature detector               |

| RTDS  | Real Time Digital Simulator                   |

| RTN   | return-to-normal                              |

| RTU   | remote terminal unit                          |

| SAE   | Society of Automotive Engineers               |

| SCADA | supervisory control and data acquisition      |

| SDG&E | San Diego Gas & Electric Company              |

| SDI   | sum of difference current                     |

| SE    | single ended                                  |

| SER   | Sequential Events Recorder                    |

| SFRA  | sweep frequency response analysis             |

| SMV   | sampled measured value                        |

| SNTP  | Simple Network Time Protocol                  |

| SOE   | Sequence of Events                            |

| SOTF  | switch onto fault                             |

| ТСР   | Transmission Control Protocol                 |

| THD   | total harmonic distortion                     |

| THDI  | total harmonic distortion, aggregated current |

| THDV  | total harmonic distortion, aggregated voltage |

| TOD   | time of day                                   |

| TWFL  | traveling-wave fault location                 |

| UCA   | Utility Communications Architecture           |

| UDP   | User Datagram Protocol                        |

| UF    | underfrequency                                |

| UL    | Underwriters Laboratories                     |

| U.S.  | United States                                 |

| UTC   | Coordinated Universal Time                    |

| UV    | undervoltage                                  |

| VAR   | volt-ampere reactive                          |

|       |                                               |

| VFD   | variable-frequency drive                        |

|-------|-------------------------------------------------|

| VR    | voltage regulator                               |

| VT    | voltage transformer                             |

| WAN   | wide-area network                               |

| WEP   | Wired Equivalent Privacy                        |

| WiMAX | Worldwide Interoperability for Microwave Access |

| WPA   | Wireless Protected Access                       |

| WPAN  | Wireless Personal Area Network                  |

|       |                                                 |

## **1** INTRODUCTION

The objective of SDG&E's EPIC-1, Project 5, on Smart Distribution Circuit Demonstrations, was to perform pilot demonstrations of smart distribution circuit features and associated simulation work to identify best practices for integrating new and existing distribution equipment in these circuits. The project was broken into two modules:

- Demonstration of Advanced Circuit Concepts

- Demonstration of Methodologies and Tools for Energy Storage System Assessment

This report describes the work and results for the first module on pre-commercial demonstration of advanced circuit concepts.

The focus of this project module was to perform pilot demonstrations of smart distribution circuit features in a laboratory for a set of selected test circuits. Using simulations and hardware-in-the-loop (HIL) testing, the desired features and upgrades were tested in the selected circuits to assess their suitability for widespread adoption.

The test circuits studied in this project include:

- Coastal-residential

- Urban

- Desert-rural

This report is divided into the following sections:

- Hardware and Circuit Evaluation: This section includes documentation and evaluation of products and technologies available for improved circuit design, system operation, and protection.

- Solutions Evaluation: This section assesses emerging distribution circuit solutions and operational practices for maintaining reliable and uninterrupted energy delivery.

- RTDS Modeling: This section outlines the process involved in the modeling of circuits. The data, which includes the load, line, source, and other devices connected to the circuits, were provided in the format used by Synergi Electric, which was converted to RSCAD and validated for accuracy.

- Voltage Regulator Tests: This section describes the hardware setup for the voltage regulation operation with the test settings and procedures described in detail. Real Time Digital Simulator (RTDS) tests were carried out and recommendations are made based on the observations recorded.

- Capacitor Bank Controller Tests: The automatic capacitor controller application was evaluated to determine the best times to switch the capacitor bank in or out, based on the load and voltage profiles provided by SDG&E. This section describes the hardware setup of the capacitor bank controller and the RTDS modeling of the device. Tests were carried out on the RTDS and the observations and results recorded.

- High-Impedance Fault Detection: This section describes the hardware setup of a high-impedance fault detector, including settings involved in the high-impedance fault protection of a circuit. The high-impedance fault logic was tested for scenarios involving different fault impedances, fault locations, and responses during the load profile run.

- Power Quality in Islands: System parameters, such as voltage and frequency, were observed on pre- and post-islanded scenarios in a test circuit. This section describes the synchrophasor devices used to tabulate the results for power quality tests and their interface with the RTDS.

- Voltage Support Coordination Tests: This section describes tests that were performed on the selected test circuit to study the system response and participation of the distributed energy resource (DER) and voltage regulator (VR) in regulating the system voltage. Both devices were designed in the RTDS and master controller logic was developed to control the coordination of these voltage regulation devices. The section further describes the observations and results of the DER tests.

- Findings: This section analyzes the results of the pre-commercial demonstrations performed and provides recommendations based on the analyses. The analysis performed provides inputs for improving the existing circuits for better reliability and operability.

- Recommendations: Recommendations are provided on the integration and coordination of multiple voltagecorrection devices on a larger distribution system, controlled via a central master controller. Certain modern concepts are also discussed, offering insights on how to improve the existing distribution system.

- Technology Transfer Plan: This section lays out the steps for commercial adoption of the best practices discussed in this report. The technology transfer plan describes the activities, equipment, resources involved and the required coordination between diverse groups to successfully implement the best practices commercially.

## 2 PROJECT SCOPE AND APPROACH

The goal of this project is to perform pilot demonstrations of smart distribution circuit features and associated simulations to analyze and identify best practices for integrating new and existing distribution equipment in a set of selected circuits. Using simulations and hardware testing, the desired features and upgrades are tested in the selected distribution circuits to assess their suitability for widespread adoption.

The following approach was adopted for successful completion of this project.

## 2.1 **PROJECT INITIATION MEETING**

A project initiation meeting was set up with the SDG&E stakeholders and the project team to review and finalize plans for the project including objectives, approach, deliverables, contractor staff, and existing SDG&E distribution design practices. The project was divided into three separate phases, interlinked to successfully achieve the tasks defined in the scope.

## 2.2 PHASE 1 HARDWARE AND CIRCUIT EVALUATION

Phase 1 includes the research, evaluation, and documentation of products and technologies available for improved distribution circuit design. It also includes selection of three SDG&E test circuits. Phase 1 is further divided into the following sub-tasks:

- a. Identify, evaluate, and document existing products and technologies available for improved distribution circuit design, system operation, and protection. This includes diverse topics such as time synchronization, protection, automation and control, communication, and renewables and energy storage.

- b. Assess and document emerging distribution circuit solutions for maintaining reliable and uninterrupted energy delivery. This includes topics such as advanced distribution automation control, synchrophasor-based applications, fault location, high-impedance fault detection, and dynamic line rating.

- c. Select three different test circuits: coastal, desert-rural, and urban-residential.

## 2.3 PHASE 2 CIRCUIT SIMULATION AND TESTING EVALUATION

Phase 2 includes the following sub-tasks:

- a. Convert the selected test circuits from Synergi Electric format into RSCAD and validate for accuracy. Hardware test racks were set up at the test facility.

- b. Develop test plans to perform individual devices tests for voltage regulator, capacitor bank controllers, high-impedance fault detection, and power quality in islands.

- c. Develop algorithms and a central controller-based system to perform system voltage coordination on distribution circuits between multiple voltage support devices, and the subsequent demonstration using RTDS. Additionally, recording test observations and results for all RTDS tests for further analysis.

## 2.4 PHASE 3 SMART CIRCUIT ANALYSIS AND RECOMMENDATIONS

Phase 3 includes the following sub-tasks:

- a. Describe important findings from the circuit demonstrations.

- b. Document possible enhancements to existing distribution circuits for improved circuit design and system operation.

- c. Provide recommendations on the integration and coordination of multiple voltage correction devices on a larger distribution circuit, controlled via a central master controller.

- d. Create a technology transfer plan to bridge the gap between the laboratory demonstration of improved distribution practices and its successful commercial and practical implementation in the field on larger distribution circuits.

- e. Discuss modern solutions to improve the operational capabilities of existing distribution circuits.

## 2.5 **PROJECT DELIVERABLES**

The project deliverables were defined at the time of the project initiation meeting. The following list includes the project deliverables that were shared with the entire team for review and feedback at the task completion.

- Functional Design Specification Describes the project scope and approach.

- Phase 1 interim report At the completion of Phase 1.

- Phase 2 interim report At the completion of Phase 2.

- Phase 3 interim report At the completion of Phase 3.

- Real Time Digital Simulator (RTDS) test plans.

- Technology transfer plan.

- Final report A comprehensive version of the above-mentioned deliverables.

- Selected circuits simplified one-line diagrams, and load and line sheets used for transferring data from Synergi Electric to RSCAD for the three selected circuits.

- RTDS models Draft, RunTime, and load scheduler modules were used for the following three circuits modeled in RSCAD:

- Coastal-residential

- Urban

- Desert-rural

- Project initiation meeting presentation.

- Phase 1 stakeholder presentation.

- Phase 2 stakeholder presentation.

- Phase 2 additional test results presentation.

- Phase 3/Final stakeholder presentation.

- Weekly/bi-weekly meeting minutes.

Bi-weekly meetings were conducted between the project teams to discuss the progress and concerns, if any. Face-toface meetings were conducted at the end of each phase with SDG&E stakeholders and the project team members to review the completed tasks and discuss the remainder of the plan.

## **3 HARDWARE AND CIRCUIT EVALUATION**

This section includes documentation and evaluation of products and technologies currently available for improved distribution circuit and design, system operation and protection. The broad discussion of available products in this section provides groundwork for the pre-commercial demonstrations in this project.

Note: Appendix E - Proprietary Information includes a look-up table for the vendors referred to in this report.

## 3.1 TIME SYNCHRONIZATION

Standard clock time is inherently inaccurate and presents added complexity in a distributed system in which several devices require precise synchronization with global time. Several protocols have been developed to control and monitor system time as the need for precise synchronization has increased across industries. The following protocols will be discussed:

- Network Time Protocol

- Simple Network Time Protocol

- Inter-Range Instrumentation Group time code format B

- Precision Time Protocol

## 3.1.1 <u>Network Time Protocol</u>

Network Time Protocol (NTP) synchronizes time across an internet protocol (IP) network. It uses Port 123 as source and destination, and runs over the User Datagram Protocol (UDP). The NTP network generally uses a time source device attached to the main time server that distributes time across the network. NTP works well over local-area networks (LANs) and wide-area networks (WANs). It requires little hardware and provides accuracies typically within a millisecond on LANs and a few milliseconds on WANs. NTP configurations typically use multiple redundant servers and diverse network paths to achieve accuracy and reliability. No more than one NTP transaction per minute is necessary to achieve a 1-millisecond synchronization on a LAN. For larger systems, NTP can routinely achieve 10-millisecond synchronization. Many NTP clients run on non-real-time operating systems such as Windows or Linux. On the Windows operating system, clock corrections of 10 to 50 milliseconds are common because the system is performing tasks deemed more important than time-keeping. Therefore, accuracy cannot be guaranteed.

## 3.1.2 Simple Network Time Protocol

Some devices support only Simple Network Time Protocol (SNTP), which is a simplified, client-only version of NTP. SNTP-enabled devices cannot be used to provide time to other devices; they can receive time only from NTP servers. The SNTP-enabled devices can achieve synchronization levels within 100 milliseconds.

## 3.1.3 IRIG-B Protocol

The Inter-Range Instrumentation Group time code format B (IRIG-B) was developed by the Inter-Range Instrumentation Group, which is the standards body of the Range Commanders Council of the United States (U.S.) military. The latest version of the IRIG-B standard was published in 2004. IRIG-B has a pulse rate of 100 per second with an index count of 10 milliseconds over its 1-second time frame. It contains time-of-year and year information in a binary-coded decimal (BCD) format, and seconds-of-day information in straight binary seconds. IRIG-B can achieve accuracy in the range of 1 to 10 microseconds.

Year information was not specified in the IRIG-B standard before the 2004 revision. The Institute of Electrical and Electronics Engineers (IEEE) previously adopted a standard (IEEE 1344, IEEE Standard for Synchrophasors for Power Systems) that included year data as part of the IRIG-B signal. This variation came to be known as IEEE 1344 extensions.

IEEE 1344 extensions use extra bits of the control functions portion of the IRIG-B time code. Within this portion of the time code, bits are designated for additional features, including:

- Calendar year (BCDYEAR)

- Leap seconds and leap seconds pending

- Daylight-saving time (DST) and DST pending

- Local time offset

- Time quality

- Parity

- Position identifiers

To use these bits of information, power system devices and other equipment receiving the time code must be able to decode them.

An IRIG-B time signal can be modulated (over a carrier signal) or unmodulated (no carrier signal), also known as dc level shift (DCLS) in the IRIG-B standard. In some manufacturers' literature, the term "demodulated" is used to describe a DCLS. However, in most cases it may be assumed the term is synonymous with unmodulated.

The IRIG-B protocol would appear the better choice, offering accuracy of 1 to 10 microseconds. Because IRIG-B systems use dedicated coaxial timing cabling between dedicated hardware clocks, the system has disadvantages. Most notable are the added expense of additional hardware and the increased time skew because of the additional physical infrastructure.

## 3.1.4 <u>Precision Time Protocol</u>

Since IEEE 1588-2008, the IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems was established, Precision Time Protocol (PTP) has addressed the clock synchronization requirements of measurement and control systems by improving accuracy and reducing cost. Among the advantages of PTP is the protocol's use of the most readily available means for network connectivity: IP over Ethernet. Taking advantage of existing Ethernet infrastructure allows considerable reuse of in-place hardware and cabling, helping reduce costs for the physical layer. PTP eliminates Ethernet latency and jitter issues through hardware time-stamping to cancel out a measured delay between nodes at the physical layer of the network. Accuracy in the range of 10 to 100 nanoseconds can be achieved with this protocol.

IEEE 1588 specifies a protocol to synchronize independent clocks running on separate nodes of a distributed control system to a high degree of accuracy and precision. The clocks communicate with each other over a communications network. In its basic form, the protocol is intended to be administration free. The protocol generates a master-slave relationship among clocks in the system by determining which of the possible sources has the better accuracy. All clocks ultimately derive their time from a clock known as the grandmaster clock. Once all clocks in a control system are synchronized, events monitored in the control system can be time stamped to a very high degree of accuracy.

## 3.1.5 <u>Applications</u>

Most relays and devices used in the power system network typically support NTP, SNTP, and IRIG-B. PTP implementation in power system devices is at a relatively nascent stage, and most of them do not support the protocol. For applications in which time-stamping is critical, IRIG-B is preferable. For applications in which cost is a factor and time-stamping with microsecond accuracy is not a factor (e.g., data storage in a distribution system), NTP/SNTP may be used.

## 3.2 **PROTECTION, AUTOMATION, AND CONTROL**

## 3.2.1 Dynamic Voltage Controller

In the wake of an increased global demand for energy and the realization of the harmful effects (and scarcity) of fossil fuels, there have been advances in renewable energy technology. The steady increase in the amount of photovoltaic power stations and wind farms around the world is testament to the growth of renewable energy as a paradigm shift from the use of fossil fuels. However, renewable energy is still an emerging technology and is not free of issues. One such issue with several grid-tied renewable energy sources is the impact on power quality and system operation.

In an ideal world, power distribution companies should provide customers with a smooth sinusoidal voltage with a fixed amplitude and frequency. Unfortunately, the output power for most renewable energy sources is highly variable; wind generators can produce rated power only when the wind is blowing and the efficiency of photovoltaic solar installations are affected by the presence of clouds. These variations associated with these energy sources result in voltage fluctuations and decreases the power quality of the overall system.

In addition to grid-tied renewable energy sources, the rise of non-linear loads causes voltage sags, swells, and surges on utility lines that affect power quality. Of these voltage disturbances, voltage sags most commonly affect power quality. Voltage sags can cause damage to industrial devices such as variable-frequency drives (VFDs), robotics, controller power supplies, and control relays. Fortunately, these issues associated with voltage stability and power quality can be alleviated with proper voltage regulation.

The dynamic voltage regulator (DVR) is the most effective device for voltage regulation and improved power quality in a system. The DVR is a series compensator used to mitigate voltage sags and to restore the load voltage to its rated value. It is normally installed in a distribution system between the supply and a critical load feeder at the point of common coupling (PCC). Its primary function is to boost the load-side voltage in the event of a voltage sag to avoid power disruption to the load. The DVR can also have features such as line voltage harmonics compensation, reduction of transients in voltage, and fault current limitations.

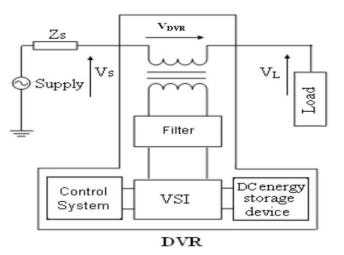

The DVR is a power electronic converter-based device capable of protecting sensitive loads from most supply-side disturbances. The general configuration of a DVR is shown in Figure 3.1 [1].

Figure 3.1: DVR General Configuration

### 3.2.1.1 MODES OF OPERATION

The DVR has three modes of operation:

- 2. Protection mode

- 3. Standby mode

- 4. Injection/Boost mode

#### 3.2.1.1.1 PROTECTION MODE

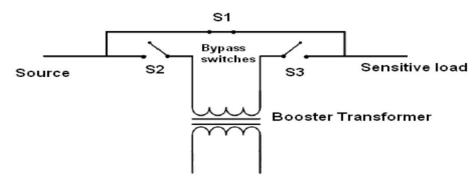

If the current on the load side exceeds a permissible limit because of a short circuit on the load side or a large inrush current, the DVR will be isolated from the system by using bypass switches as shown in Figure 3.2 [1]. Switches S2 and S3 will open and S1 will be closed to provide an alternative path for the load current to flow.

Figure 3.2: Protection Mode

## **3.2.1.1.2 STANDBY MODE**

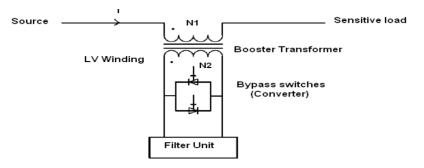

In Standby mode, the low-voltage winding on the booster transformer is shorted through the converter as shown in Figure 3.3 [1]. No switching of semiconductors occurs in this mode, and the full-load current will pass through the transformer primary.

Figure 3.3: Standby Mode

## 3.2.1.1.3 <u>INJECTION/BOOST MODE</u>

In Injection/Boost mode, the DVR injects a compensating voltage through the booster transformer after the detection of a disturbance in the supply voltage.

## 3.2.1.2 DVR VOLTAGE INJECTION METHODS

The four methods of DVR voltage injection are discussed below. The choice of method depends on several limiting factors such as DVR power rating, load conditions, and voltage sag type.

- Pre-sag/dip compensation method: Tracks the supply voltage continuously for disturbances. If a disturbance is detected, the DVR will inject the difference in voltage between the voltage sag and the ideal prefault condition. The active power injected by the DVR cannot be controlled and is determined by external conditions such as the type of fault and load conditions.

- In-phase compensation method: The injected voltage is in phase with the point-of-contact voltage regardless of the load current and prefault voltage. The phase angles of the pre-sag and load voltage are different; however, attention is placed on maintaining a constant voltage magnitude on the load.

- In-phase advanced compensation method: Reduces the real power spent by the DVR by decreasing the power angle between the sag voltage and the load current. Active power is injected into the system by the DVR during disturbances; this active power is limited to the stored energy in the dc link of the DVR. The minimization of injected energy is achieved by making the injection voltage phasor perpendicular to the load current phasor.

- Voltage tolerance method: Voltage magnitude variations between 90 percent and 100 percent of the nominal voltage and phase angle variations between 5 percent and 10 percent of the normal state will not disturb the operation characteristics of loads. This method helps maintain the load voltage within the tolerance area with small changes in voltage magnitude.

### 3.2.1.3 DYNAMIC VOLT-AMPERE REACTIVE COMPENSATION SOLUTION

Vendor A dynamic volt-ampere reactive (D-VAR) was found to be a cost-effective way to provide continuous voltage regulation, improve voltage stability, meet interconnection requirements, and dynamically provide grid support where it is needed.

The main features of the D-VAR system include:

• High-speed response to voltage disturbances: D-VAR systems stabilize and regulate voltage and power factors on transmission and distribution networks and at industrial operations. The system detects and

rapidly compensates for voltage disturbances by injecting leading or lagging reactive power at key points on transmission and distribution grids. Each D-VAR system is tailored to meet specific customer requirements and accommodate changing grid conditions.

- Compliant with utility interconnection requirements: The D-VAR system can assist wind and solar generation plants in meeting utility interconnection requirements, including low-voltage ride-through (LVRT) and high-voltage ride-through (HVRT) regulation and power factor correction. The system helps reduce stress on equipment and extends its life by mitigating transient voltage events and by soft-switching capacitors and reactor banks with propriety and patented technology.

- Modular, scalable, compact, and flexible: D-VAR systems are highly modular and scalable by design. Each unit is compact to accommodate areas with space constraints. This allows utilities to install properly sized systems in the most effective power grid locations and quickly augment capability as demands increase.

## 3.2.1.4 D-VAR SYSTEM SPECIFICATIONS

The technical specifications of the D-VAR system (as listed on the datasheet) are shown in Table 3.1.

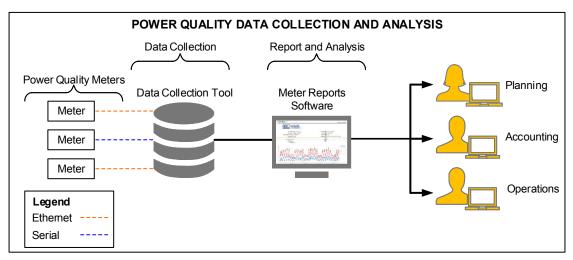

| Connection                | Medium Voltage (up to 46 kV)                                                                                     |